The mnemonics for machine operation codes as printed in this manual are considered acceptable but non-standard by UNIVAC. This means that:

1. The UTMOST processor will accept programs written using either this set of mnemonics or the standard UNIVAC III set.

or,

2. A program will be furnished which will convert source programs with the non-standard mnemonics to source programs containing standard mnemonics.

The following table gives the relationship between standard and non-standard mnemonics:

| SALT<br>(standard) | UTMOST<br>(non-standard) |

|--------------------|--------------------------|

| $\mathbf L$        | LA                       |

| LCS                | LAN                      |

| EXT                | LF                       |

| ST                 | SA                       |

| STCS               | SAN                      |

|                    | SZ                       |

| A                  | DA                       |

| S                  | DS                       |

| AH                 | DAH                      |

| SH                 | DSH                      |

| M                  | DM                       |

| D                  | DD                       |

| BA                 | BA                       |

| BAH                | BAH                      |

| BS                 | BS                       |

| BSH                | BSH                      |

| SR                 | DSR                      |

| SL                 | DSL                      |

| SAR                | ASR                      |

| SAL                | ASL                      |

| SBC                | BRR                      |

| CA                 | CM                       |

| C                  | C                        |

| CONE               | CPA                      |

| CZRO               | CPZ                      |

| TEQ                | JE                       |

| THI                | JG                       |

| TLO                | JL                       |

| TPOS               | JP                       |

| TUN                | J                        |

| TR                 | SLJ                      |

| SSI                | SS                       |

| RSI                | RS                       |

| TSI                | JS                       |

| SALT<br>(standard)       | UTMOST<br>(non-standard) |

|--------------------------|--------------------------|

| ATD                      | LAD                      |

| DTA                      | SAA                      |

| ZUP                      | LAE                      |

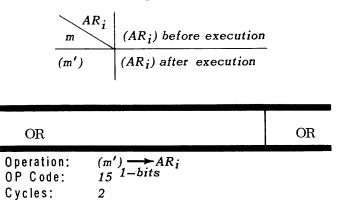

| SUP                      | OR                       |

| ERS                      | AND                      |

| LX                       | LX                       |

| STX                      | SX                       |

| IX                       | IX                       |

| ICX                      | IXC                      |

| TCI                      | TC                       |

| RCI                      | RC                       |

| TPE                      | TPE                      |

| RPE                      | RPE                      |

| TIO                      | TIO                      |

| TIO<br>TIO               | TW<br>TR                 |

| TCI                      | TOV                      |

| TCI                      | TOP                      |

| RIO                      | RIO                      |

| RIO                      | RW                       |

| RIO                      | RR                       |

| AIO                      | AI                       |

| PIO                      | PI                       |

| TIOP                     | JIP                      |

| IOF                      | LC                       |

| IOF                      | LWC                      |

| IOF                      | LRC                      |

| NOP                      | NOP                      |

| STMC                     | SC                       |

| TR*                      | SCJ                      |

| STMC                     | SL                       |

| STMC                     | SWC                      |

| STMC                     | SRC                      |

| STCR                     | ST                       |

| STCR                     | SRT                      |

| STCR                     | SWT                      |

| WAIT                     | HJ                       |

|                          | RCK                      |

| DIS                      | WD<br>R <b>T</b>         |

| R <b>T</b><br>W <b>T</b> | RT<br>WT                 |

| ACT                      | AT                       |

| AOT                      | AL                       |

An assembler directive will be supplied for specifying the desired set of mnemonics. The method of accomplishing this will be specified later.

-

Manual Number: N? 01047

## UNIVAC III UTMOST

## MANUAL REGISTRATION SHEET

| CHARGE TO: | NAME    |

|------------|---------|

|            | BRANCH  |

|            | ADDRESS |

|            |         |

|            |         |

|            | DATE    |

This registration entitles the holder of this manual to receive all updating materials.

Remove this sheet and supply the above information. Immediately mail to:

MANAGER, PROGRAM LIBRARY SERVICES UNIVAC 315 PARK AVENUE SOUTH NEW YORK 10, NEW YORK

Nº 01047

| REVISION:    | SECTION: |

|--------------|----------|

|              | Index    |

| DATE:        | PAGE:    |

| July 1, 1962 | 1        |

## TABLE OF CONTENTS

| I. | INTF                                            | TRODUCTION                                                                                                                     |                                                                |  |  |

|----|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|

| п. | BASIC INTRODUCTION TO UTMOST ASSEMBLER LANGUAGE |                                                                                                                                |                                                                |  |  |

|    | 1.                                              | Computers and Languages                                                                                                        | II - 1                                                         |  |  |

|    | 2.                                              | The UTMOST Assembler                                                                                                           | II - 2                                                         |  |  |

|    | 3.                                              | . Symbolic Coding Format                                                                                                       |                                                                |  |  |

|    |                                                 | <ul> <li>a. Label Field</li> <li>b. Operation Field</li> <li>c. Operand Field</li> <li>d. Line Control</li> </ul>              | II - 3<br>II - 4<br>II - 5<br>II - 6                           |  |  |

|    | 4.                                              | Expressions                                                                                                                    | II – 7                                                         |  |  |

|    |                                                 | <ul><li>a. Elementary Items</li><li>b. Operators</li></ul>                                                                     | II - 7<br>II - 12                                              |  |  |

|    | 5.                                              | Data Word Generation                                                                                                           | П - 18                                                         |  |  |

|    |                                                 | <ul> <li>a. ICW, Increment and Compare Word</li> <li>b. TWC, Two Word Constants</li> <li>c. + or - Operation Fields</li> </ul> | II - 18<br>II - 18<br>II - 19                                  |  |  |

|    | 6.                                              | . Mnemonic Instructions                                                                                                        |                                                                |  |  |

|    | 7.                                              | Line Items                                                                                                                     |                                                                |  |  |

|    | 8.                                              | Assembler Directives                                                                                                           | II - 25                                                        |  |  |

|    |                                                 | <ul> <li>a. EQU</li> <li>b. RES</li> <li>c. USE</li> <li>d. FORM</li> <li>e. SET</li> <li>f. FLD</li> </ul>                    | II - 26<br>II - 26<br>II - 27<br>II - 28<br>II - 30<br>II - 31 |  |  |

| UNIVAC III |  |

|------------|--|

|------------|--|

| REVISION:    | SECTION: |  |

|--------------|----------|--|

|              | Index    |  |

| DATE:        | PAGE:    |  |

| July 1, 1962 | 2        |  |

## TABLE OF CONTENTS (Cont'd)

|      |     | <ul> <li>g. END</li> <li>h. DO</li> <li>i. PROC</li> <li>j. NAME</li> <li>k. Procedure Reference Lists</li> </ul> | II - 31<br>II - 32<br>II - 33<br>II - 35<br>II - 36 |

|------|-----|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|      | 9.  | Sample Problem                                                                                                    | II - 41                                             |

|      | 10. | Sample Floating Dollar Sign Editing Procedure                                                                     | II - 44                                             |

|      | 11. | Sample MOVE Procedure                                                                                             | II - 50                                             |

| III. | PRO | GRAMMER'S REFERENCE GUIDE                                                                                         | III - 1                                             |

|      | Α.  | Line Control                                                                                                      | III - 1                                             |

|      | В.  | Label Field                                                                                                       | III - 1                                             |

|      | C.  | Operation Field                                                                                                   | III - 1                                             |

|      | D.  | Operand Field                                                                                                     | III - 2                                             |

|      | Ε.  | Expressions                                                                                                       | III - 2                                             |

|      | F.  | Mnemonic Instructions                                                                                             | III - 5                                             |

|      | Н.  | Line Item                                                                                                         | III - 5                                             |

|      | I.  | Addressing                                                                                                        | III - 7                                             |

|      | J.  | Assembler Directives                                                                                              | III – 7                                             |

|      | К.  | Procedure Reference Line                                                                                          | III - 11                                            |

|      | L.  | Inter-Program Communication                                                                                       | III – 11                                            |

| UNIVAC | ΠU | TMOST |

|--------|----|-------|

|--------|----|-------|

## TABLE OF CONTENTS (Cont'd)

| IV.  | OPERATING PROCEDURES         | IV -  | 1 |

|------|------------------------------|-------|---|

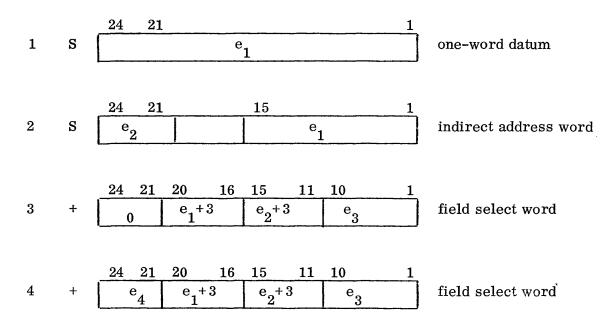

| v.   | UNIVAC III CENTRAL PROCESSOR | V -   | 1 |

| VI.  | BOSS III COMMUNICATIONS      | VI -  | 1 |

| VII. | MNEMONIC INSTRUCTIONS        | VII - | 1 |

|                   | REVISION:             | SECTION:       |

|-------------------|-----------------------|----------------|

| UNIVAC III UTMOST | DATE:<br>July 1, 1962 | Notes<br>Page: |

| U | IN | IV | Ά | Ш | UTM | NOST |

|---|----|----|---|---|-----|------|

|---|----|----|---|---|-----|------|

| REVISION:    | SECTION: |

|--------------|----------|

|              | I        |

| DATE:        | PAGE:    |

| July 1, 1962 | 1        |

#### I. INTRODUCTION

UTMOST (UNIVAC THREE MACHINE ORIENTED SYMBOLIC TRANSLATOR) is an easy to learn and easy to use assembly language designed to permit rapid efficient coding for UNIVAC III. UTMOST is a two-pass assembly system providing rapid translation from symbolic to object coding.

The UTMOST system contains a wide and sophisticated variety of operators which provide the ability to fabricate fields during assembly without restrictions on the programmer. The mnemonic operation codes describe machine functions and prevent the programmer from having to learn a wide variety of octal machine codes. The system has a series of ten assembly directing instructions which aid greatly in promoting easy communication with input-output and executive systems. In addition, the assembly directives provide the programmer with the ability to write short routines which are variable at assembly time. These routines and standard routines are easy to incorporate in the program, thereby reducing the effort of the programmer and increasing programming production.

UTMOST produces relocatable binary output in a card form suitable for processing by a binary card loader. It also supplies a listing of the original symbolic coding together with an octal representation of the word generated. Certain error flags are also supplied in the listing.

The UTMOST manual is in several sections. Section II is designed to aid the programmer unfamiliar with this type of system. Section III is designed to act as a brief programmers' reference guide to the UTMOST system.

## II. A BASIC INTRODUCTION TO THE UTMOST ASSEMBLER LANGUAGE

### A. GENERAL

#### 1. Computers and Languages

In order to solve a problem, a computer must be given a series of instructions which determine how the computer is to operate. In addition, the computer must be given one or more sets of data upon which to operate. This combination of instructions and data is called a program. A program must define in complete detail exactly what the computer is to do, under every conceivable combination of circumstances, with the data which is read into or processed by the computer. The number of instructions required for the complete solution of a problem may be a few hundred or many thousands, depending upon the problem. The computer may refer to these instructions one after another. It can also be instructed to repeat, modify, or skip over certain instructions, depending upon intermediate results or circumstances. The ability to repeat operations, usually called looping, combined with other facilities of modifying and skipping over instructions, permits a significant reduction in the number of instructions required to perform a given job. For example, two sets of numbers exist and it is desired to add the corresponding numbers of each set together. Instructions may be written to add the first number of the first set to the first number of the second set, then to repeat this operation with the second, third, fourth, etc., numbers of each set. In this way, a few instructions may cause thousands of additions.

Since the computer does not respond to the English language, the program must be encoded in a form known as <u>machine language</u>. Considerable time and effort have been expended in developing programming systems that allow the programmer to write in a <u>symbolic language</u> more easily comprehensible to him than machine language. Associated with a programming system is a machine language program called a processor. The processor accepts a program written in the symbolic language (source program) and converts it into a machine language program (object program). The symbolic language utilized to program for UNIVAC III is known as UTMOST (Univac Three Machine Oriented Symbolic Translator).

### 2. The UTMOST Assembler

The UTMOST assembly program was designed to provide a programmer with an easy to learn and easy to use assembly system. UTMOST is a straightforward data processing program, accepting input data (symbolic coding) and processing it and producing as system output, object coding usable by UNIVAC III directly.

As the symbolic coding is processed, the UTMOST assembler tallies the number of lines produced in a location counter. The location counter can be referenced by the programmer in his symbolic coding and may be utilized throughout his program. UTMOST also provides the programmer with a series of 'operators' permitting him to fabricate any object code values which he may need. A small number of extremely powerful assembly directives are also made available which allow the programmer to direct the assembly in an extremely positive manner during the actual assembly. In addition, the programmer may use mnemonic operation codes which explain machine functions by their very nature rather than having to learn the machine code bit configurations.

The UTMOST assembler provides output in the form of a loadable object program plus a listing of the symbolic program and the object program. The listing also provides the programmer with error flags at whatever points the assembly system detected the errors.

In the section following, each feature of the UTMOST assembly system is examined in detail with examples of each operation, as well as an illustrative problem demonstrating a legitimate approach to the solution of a simple data processing problem for UNIVAC III utilizing the UTMOST language.

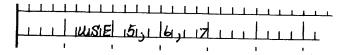

#### 3. Symbolic Coding Format

In writing a program in UTMOST symbolic language, the programmer is primarily concerned with three fields, a label field, operation field and operand field. In addition, it is possible to annotate the symbolic language at the time it is written through the use of comments which will provide clarity for the programmer and relate the coding to its associated flowchart.

| REVISION:    | SECTION: |

|--------------|----------|

|              | II       |

| DATE:        | PAGE:    |

| July 1, 1962 | 3        |

In writing in UTMOST language, the programmer is not bound by a fixed length field concept as is the case with older assembly languages. All of the fields in UTMOST are in free form, and are designed to provide the greatest convenience possible for the programmer.

| PROGRAM           |              | PROGRAMME | ER                | DATE           | PAGEOF             | PAGES |

|-------------------|--------------|-----------|-------------------|----------------|--------------------|-------|

| LABEL & OPERATION | Δ Ο          | PERAND    | Δ                 | COMMENTS       | 72 73              | 80    |

|                   | ILLI         |           | 1 1 1 1 1 1 1 1 1 |                |                    |       |

|                   |              |           | Juliuluul         |                |                    |       |

|                   | <u>ulu</u> l |           |                   |                |                    |       |

|                   |              |           |                   |                |                    |       |

|                   |              | <u> </u>  |                   |                | <u>n ludul lul</u> |       |

|                   |              |           |                   |                |                    |       |

|                   |              | 111111111 | Indud             |                |                    |       |

|                   |              |           |                   |                |                    |       |

|                   |              |           |                   |                |                    |       |

| · · · · ·         | utuit        |           |                   |                |                    |       |

| 1                 |              |           |                   | ' ' <u>u</u> l | 1111111111111111   |       |

|                   | · į          |           |                   | I              |                    | ·     |

|                   |              |           |                   |                | 1 I                |       |

#### a. Label Field

A label is a method of identifying either a symbolic line of coding, or a word of data. In writing a label in UTMOST, the programmer may use any meaningful combination of one to eight characters. Of these eight characters, the first must be an alphabetic (A...Z), and the others, if present, may be either alphabetics or numerics (0-9). Sample labels are listed below:

| PRNT | ARRANGE |

|------|---------|

| ONE  | ADOL    |

| А    | OVER2   |

In writing a label in the label field of a symbolic line, the first character of the label must be left justified within the line and the field terminated by a blank. There must be no blanks within the label field itself. When the label is analyzed by the UTMOST assembly program, it is equated to the current value of the location counter except in the cases of a label associated with the EQU, FORM, DO, FLD, PROC and NAME assembly directives. Each of these special cases is discussed separately in the portions of the manual dealing with the specific directive.

| REVISION:    | SECTION: |  |  |

|--------------|----------|--|--|

|              | п        |  |  |

| DATE:        | PAGE:    |  |  |

| July 1, 1962 | 4        |  |  |

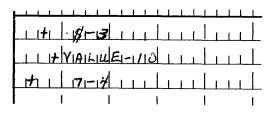

| LABEL     | - Δ  | OPERA | TION       |             | Δ   | C | <b>DPER</b> | AND |  |

|-----------|------|-------|------------|-------------|-----|---|-------------|-----|--|

| ONER      | NOF  |       | 111        |             |     |   |             |     |  |

|           |      |       |            |             |     |   |             |     |  |

| ONEL      |      | 15, 1 | <u>6</u> 1 | <u>   .</u> |     |   |             |     |  |

|           |      |       |            |             |     |   |             |     |  |

| ARIBIANIC | EL L | ILA.  | 17         | 123         | ·L. |   |             |     |  |

In the symbolic lines illustrated above, each of the labels in the label field, OVER, ONE and ARRANGE follow the requirements of the label field. Each starts with an alphabetic in column 1, is from one to eight characters in length, and is terminated by a space.

### b. Operation Field

The operation field of a symbolic line informs the assembler of the purpose of the line. An operation field may be up to eight characters in length, and may contain a mnemonic machine operation code, an assembler directive, a label associated with a FORM NAME or PROC directive or a data generating code. Each of the above categories will be discussed in detail in its appropriate section.

An entry in the operation field is terminated by a blank unless it is a plus or minus sign, in which case the operand field may begin in the succeeding column. If the line does not have a label, the operation field may begin in the second column of the coding form.

If an operation field contains an assembler directive other than RES (which increments the location counter), the location counter will not be affected. In all other cases, the location counter will be incremented by one after the line has been generated.

| REVISION:    | SECTION: |  |  |

|--------------|----------|--|--|

|              | II II    |  |  |

| DATE:        | PAGE:    |  |  |

| July 1, 1962 | 5        |  |  |

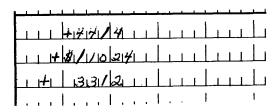

| LABEL       | Δ     | OPERATION             |          | Δ | OPERA | 1D |

|-------------|-------|-----------------------|----------|---|-------|----|

| ØMEI LAI    | 1 151 | 18 11                 |          |   |       |    |

| 101M 11151; | 131   | 1 71111               |          |   |       |    |

| RESI        |       | 312 111               | 11-      |   |       |    |

| 11111       | 18E   | <u>اراحنا زا ۱۱ ا</u> | <u>3</u> |   |       |    |

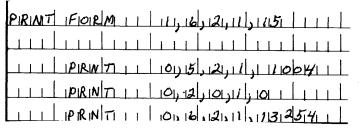

In the illustration of operation fields above, Line 1 contains an operation field LA following the label ONE.

Line 2 contains an operation field, CM, starting in column 2, showing that no label is present.

Line 3 contains an assembler directive as an operation field, RES.

Line 4 also contains an assembler directive in the operation field, USE.

Note that each operation field follows the rules stated above.

### c. Operand Field

The operand field of a symbolic line follows the label and operation fields. It consists of one or more expressions defining the information required by the operation field of the line.

Expressions within the operand field are separated by commas, and the comma indicates that another expression follows. Termination procedures are discussed under Line Control, below. The maximum number of expressions on a line is determined by the content of the operation field of the line. However, any line may contain less than the maximum number of expressions indicated by the operation field; so long as it has at least one. The unwritten expressions will be assumed by the assembler to be zero.

| REVISION:    | SECTION: |  |  |

|--------------|----------|--|--|

|              | п        |  |  |

| DATE:        | PAGE:    |  |  |

| July 1, 1962 | 6        |  |  |

| LABEL    | Δ  | OPERAT   | ION | Δ                | OPER | AND |

|----------|----|----------|-----|------------------|------|-----|

| ILA OIII |    |          |     |                  |      |     |

|          | 71 | ا الخارا |     |                  |      |     |

|          |    |          |     | <u>     </u><br> |      |     |

In the examples, the 0 following LA represents a single expression in the operand field. The second line of symbolic coding represents a three expression operand field, each expression separated from the previous one by a comma.

d. Line Control

The information content of a line to the assembler consists of a label, operation, and operand fields. The information content is normally terminated when the maximum number of expressions required by the operation have been encountered (or maximum number of lists in the case of a procedure reference, or by column 72, whichever occurs first. There are two special marks which override the normal rule:

- 1) Continuation: If a ";" is encountered outside of an alphabetic item, the current line is continued with the first nonblank on the following line and there is no more information to the assembler on the line in which the ";" occurred.

- 2) Termination: If a "." followed by a blank is encountered outside of an alphabetic item, the line is terminated at this point. If additional expressions are required by the operation field, they are assumed by the assembler to be zero.

A continuation or termination mark may occur anywhere on a line. Following the information control of a line, any characters may be entered.

| REVISION:             | SECTION:   |

|-----------------------|------------|

|                       | II         |

| date:<br>July 1, 1962 | PAGE:<br>7 |

|                       |            |

| 1   | LABEL    | Δ  | OPERATION | Δ | OPERAND         |

|-----|----------|----|-----------|---|-----------------|

| LIA | BIELIFIC |    |           |   |                 |

| M   |          | ĻĹ |           |   |                 |

| Т   | 2141     |    |           |   |                 |

|     |          |    |           |   | 1 1 1 1 1 1 1 1 |

The semicolons indicate that the line is continued on the next line. The assembler would treat the three lines as though they were the following line.

| KABIELI IEKRIM 11,12141 ITHIZALILIINELIIS TERMINIATIEN BYLTIHE PERILAD SAMOL    |

|---------------------------------------------------------------------------------|

| - TITHIS WIME IS ALSO TERMINATED BY THE PERMICE                                 |

| - MINDI MILLANA INE IPRINTIEDI IONI TIHE ISYMBOLALIKI MISTILA GIOMANYI I IIIIII |

| llll                                                                            |

The three lines above use a period followed by a space to terminate the lines. Any information following the period space is considered to be a comment and will be printed on the symbolic output listing. The assembler will take no action on the information following the period.

### 4. Expressions

An expression is an elementary item or a series of elementary items connected by operators. It normally appears in the operand field of a symbolic line.

### a. Elementary Items

UTMOST permits the utilization of a series of elementary items which may be used in expressions.

Label: Any label may be used as an elementary item. The structure of a label corresponds to the description of the label field discussed earlier. A label may be from one to eight characters in length, the first of which must be an alphabetic. When a label has been encountered in the label field of a symbolic line (with exceptions

| REVISION:    | BECTION: |  |  |

|--------------|----------|--|--|

|              | п        |  |  |

| DATE:        | PAGE:    |  |  |

| July 1, 1962 | 8        |  |  |

|              | DATE:    |  |  |

noted under Label Field), it is assigned the current value of the location counter. Thereafter, when it is encountered within an expression, the integer value initially assigned to it will be substituted for the label within the expression.

| 111 191 23145 6171 |

|--------------------|

Various sample labels are illustrated above as they would appear as elementary items in the operand field.

### 2) Location:

The current value of the location counter may be used as an elementary item within the operand field of a symbolic line. The format of a reference to the location counter is the dollar sign (\$). When this sign appears in an expression, the value of the location counter is substituted for it. It is useful in reflexive addressing.

| 111 1 |  |

|-------|--|

|       |  |

In the example above, if the current value of the location counter was 5280, the integer value 5280 would be substituted for the dollar sign (\$) in its expression, and right justified within the object field.

3) Octal: Octal values (base eight) may be represented in expressions as elementary items by preceding the desired value with a zero. The assembler will convert these values to their corresponding binary (base two) equivalents. The converted binary integer will be right justified in its object coded field.

| UNIVAC | Ш | UTMOST |

|--------|---|--------|

|--------|---|--------|

| REVISION:    | SECTION: |

|--------------|----------|

|              | п        |

| DATE:        | PAGE:    |

| July 1, 1962 | 9        |

In the examples above:

017 is equivalent to 000 000 000 000 000 000 001 111 07007 is equivalent to 000 000 000 000 111 000 000 111 in their converted object code.

4) Decimal: Decimal values may be used as elementary items within an expression. Where they appear, decimal values (base 10) will be converted into their binary equivalents and right justified within their object fields. A decimal item is represented as a non-zero digit followed by decimal (0-9) digits.

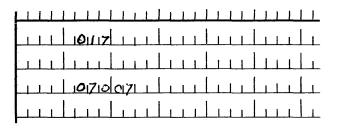

| 1111191111 |  |

|------------|--|

| 111/10/214 |  |

|            |  |

|            |  |

In the examples above:

| 9 is equivalent to    | 000000000000000000000000000000000000000 |

|-----------------------|-----------------------------------------|

| 1024 is equivalent to | 0000000000001000000000                  |

5) BCD: UNIVAC III binary coded decimal excess three values in four bit notation may be utilized in elementary items by preceding the value with a colon (:). When a decimal value appears in this format, it will be translated by the assembler into its corresponding 4 bit base 16 value and right justified within its field.

| REVISION:    | BECTION: |

|--------------|----------|

|              | II       |

| DATE:        | PAGE:    |

| July 1, 1962 | 10       |

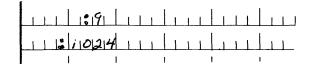

In the examples above:

| :9 is equivalent to    | 0000 | 0000 | 0000 | 0000 | 0000 | 1100 |

|------------------------|------|------|------|------|------|------|

| :1024 is equivalent to | 0000 | 0000 | 0100 | 0011 | 0101 | 0111 |

6) <u>Alphabetics</u>: Excess three six bit alphabetic characters may be represented in an elementary item by enclosing the desired characters within apostrophes ('). Since the assembler recognizes an apostrophe as the end of the alphabetic value, it is not permitted to use an apostrophe within the alphabetic grouping. The six bit object code resulting from an alphabetic item will be right justified within its field and preceded by binary zeros (space codes).

| III NIPIAKSEI'II IIIIIIIII |  |

|----------------------------|--|

|                            |  |

|                            |  |

In the example above:

'PAGE' is equivalent to101010 010100 011010 011000'Z' is equivalent to000000 000000 000000 111100

7) <u>Floating Point Numbers</u>: Floating point numbers may be represented within an elementary expression by including a decimal point (period) within the desired decimal value. the converted value will be in standard UNIVAC excess 50 floating point format with a ten digit mantissa and a two digit characteristic.

In the example above:

3.14 is equivalent to 513140000000 in 4 bit BDC digits.

8) Field: A field may be referenced as an elementary expression by writing a field label followed by an expression enclosed in parentheses representing the address of the partial word. The field item is discussed in greater detail in the section on Assembler Directives, FLD directive.

In the example above:

EXT represents the bit control pattern for field selection, (VALUE) represents the address from which the field will be selected.

- 9) <u>Parameter</u>: A parameter may exist as an elementary item by following the procedure label with one or two expressions enclosed in parentheses. The parameter item is discussed in detail under Assembly Directives, PROC directive.

- 10) <u>Line</u>: An entire line may exist as an elementary item by enclosing the line within parentheses. The assembler will generate the value of the word that the line would generate if it existed as a separately coded line.

| L |  |   |   | 1 |   | 1 | I | 1 | 1 |   | 1 |   | 1 | 1 | 1 |   | 1 |   |

|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | L |

| 6 |  |   |   |   | 1 |   |   |   |   |   |   |   |   |   |   |   |   |   |

| • |  | ' | 1 |   | , | ſ | ' | ' | 1 | , | 1 | ' | 1 | 1 | 1 | I | 1 | • |

In the above example:

('DON') would generate the constant DON in six bit excess three alphabetics preceded by binary zeros in the same manner that 'DON' would on a symbolic line by itself.

### b. Operators

An expression may consist either of an elementary item, or a series of elementary items connected by operators as shown in the table below:

- + Arithmetic Sum

- Arithmetic Difference

- \* Arithmetic Product

- / Arithmetic Quotient

- ++ Logical Sum (OR)

- -- Logical Difference (EXCLUSIVE OR)

- \*\* Logical Product (AND)

- // Covered Quotient  $(a//b = \frac{a+b-1}{b})$

- = Equals

- > Greater Than

- < Less Than

- \*+ a  $*+b = a*10^{b}$

- \*-  $a *-b = a *10^{-b}$

- + Arithmetic Sum : The arithmetic sum operator may be used to combine two or more items. The assembler will sum the integer values of the items and the resultant integer value will be utilized in the resulting expression.

|         | 17+3  |   |   |   |     |

|---------|-------|---|---|---|-----|

| 1 1 + 8 | +1/51 |   |   |   |     |

| · · · · | 1     | 1 | 1 | 1 | 1 1 |

In the above examples:

7 + 3 would produce the integer 10 in binary.

\$ + 15 would produce the current value of the location counter incremented by 15 in binary.

2) <u>- Arithmetic Difference</u>: The arithmetic difference operator may be used to subtract one item from another. The assembler will subtract the integer value of the second item from that of the first, and the resultant integer difference will be substituted in the expression.

| REVISION:    | SECTION: |

|--------------|----------|

|              | Ш        |

| DATE:        | PAGE:    |

| July 1, 1962 | 13       |

In the above examples:

\$ - 3 will produce the current contents of the location counter less three.

VALUE - 10 will produce the integer equivalent of the label "VALUE" minus ten.

7-4 will produce the integer three.

3) \* Arithmetic Product: The arithmetic product operator may be used to multiply one item by another producing the arithmetic product. The assembler will multiply the integer value of the first item by the integer value of the second item and the resultant integer value will be substituted in the expression.

|             |   |   | لسلسلسا |   |

|-------------|---|---|---------|---|

| 1 1+71-*31  |   |   |         |   |

| 1+1 1+1+121 |   |   |         |   |

|             | 1 | 1 | 1       | 1 |

In the above examples:

7\*3 will produce the integer value 21. \$\*2 will produce an integer value equivalent to the current contents of the location counter times 2.

4) / Arithmetic Quotient: The arithmetic quotient operator may be used to divide one item by another producing the arithmetic quotient. The assembler will divide the integer value of the first item by the integer value of the second item, and the resultant quotient will be utilized in the expression. The remainder is discarded by the assembler.

In the above examples:

44/4 will produce the integer value 11. \$/1024 will produce an integer value equivalent to the number of possible index registers required for area addressing in the program up to this point in the program. 33/2 will produce an integer value of 16 (remainder has been discarded).

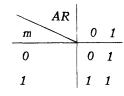

5) <u>++ Logical Sum (OR)</u>: The logical sum operator (OR) may be used to logically sum the binary equivalents of two items. The assembler will logically add the two values and the resulting logical sum will be utilized in the expression.

| ┠┵┶┶┶┶┶┶┶┶┶┶┷                           |  |

|-----------------------------------------|--|

| 141111111111111111111111111111111111111 |  |

In the above example:

'A' in six bit code is010100'3' in six bit code is000110Logical sum generated010110

6) <u>-- Logical Difference (EXCLUSIVE OR)</u>: The logical difference operator may be used to obtain the logical difference between the integer values of two items. The assembler will perform an EXCLUSIVE OR on the two items (where a bit is present in corresponding position in both items, the result is binary 0, where no bit is present in corresponding positions, the result is binary 0, where a bit is present in either one of corresponding positions, the result is 1). The resultant integer is then utilized as the value of the expression.

| REVISION:    | SECTION: |

|--------------|----------|

|              | Ш        |

| DATE:        | PAGE:    |

| July 1, 1962 | 15       |

# ┶┶┶┶┶┶┶┶┶┶┶┶┶┶┶┶ ┶┶╋┥<mark>╷┉┉┉┈┈╵╓╷╵╷╷╷╷╷╷╷╷╷</mark>

In the above example:

| 'V' in six bit code is | 111000 |

|------------------------|--------|

| 'T' in six bit code is | 110110 |

| Logical difference is  | 001110 |

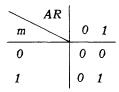

7) \*\* Logical Product (AND): The logical product operator may be used to AND (Logically multiply) the integer value of one item by another. The assembler will logically multiply the two values and the resulting logical product will be utilized in the expression.

| NVI'IXIX | 1771 |  |

|----------|------|--|

In the above example:

| 'V' in six bit code is | 111000 |

|------------------------|--------|

| 'T' in six bit code is | 110110 |

| Logical product is     | 110000 |

8) // Covered Quotient  $(a//b = \frac{a+b-1}{b})$ : The covered quotient operator may be used to divide the integer value of an item by the integer value of a second item or expression. The effect is the same as adding one to the integer value of the quotient in straight division (A/b) if there were a remainder.

The resultant integer will be utilized in the expression.

| 111(11-1517 | AIRITI) /1/10214 |   |

|-------------|------------------|---|

| F P         | 1                | I |

In the above example:

(\$-START)//1024 (where START is the first location required by the program and greater than 1024) will produce a covered quotient equivalent to the number of index registers required for area addressing up to the point where the expression appeared.

9) = Equal: The equals operator may be used to compare the integer values of two items or expressions. If the two integer values are equal, the assembler will generate a binary 1 as the resultant field. If the two integer values are not equal, the assembler will generate a binary 0 as the resultant field.

|               | 11 |

|---------------|----|

| 111 \$1708311 |    |

In the above example:

- If \$ = 7083, a value of binary 1 will be generated. If  $\$ \neq 7083$ , a value of binary 0 will be generated.

- 10) > Greater Than: The greater than operator may be used to compare the integer values of two items or expressions. If the integer value of the first item or expression is greater than the integer value of the second, the assembler will generate a binary 1 as the resultant field. If the first value is less than or equal to the second, the assembler will generate a binary 0 as the resultant field.

| 1111  | 1111  |   |   |

|-------|-------|---|---|

| AMOIL | NTITA |   |   |

| ı     | I     | ł | 1 |

In the above example:

If the value of AMOUNT is greater than 2, a binary 1 will be generated, otherwise a binary 0 will be generated.

11) < Less Than: The less than operator may be used to compare the integer values of two items or expressions. If the integer value of the first item or expression is less than the integer value of the second, the assembler will generate a binary 1 as the resultant field. If the first value is greater than or equal to the integer value of the second, a binary 0 will be generated.</p>

In the above example:

If the value of COUNT is less than 5, a binary 1 will be generated, otherwise a binary 0 will be generated.

12) \*+ Positive Exponent: The positive exponent operator may be used to create a two word floating point constant in excess 50 notation where a \* + b is equivalent to a \*10<sup>b</sup>. Both words must be excess three binary coded decimal numerics.

|   | <u></u> |   |         |        |      |    | ┹╍┸╼╋ |

|---|---------|---|---------|--------|------|----|-------|

| ; |         |   | \$ 1101 | 0171+1 | 1151 |    |       |

|   |         | l | I       | 1      | 1    | I. | 1     |

In the above example:

:10.0\*+:15 will produce 67100000000

13) \*- Negative Exponent: The negative exponent operator is similar to the positive exponent operator except that it will produce a floating point word in excess 50 notation with a characteristic from 0 to 50.

| 1 | 1 | 1 | 1 | 1 | L  |   | 1   |    |      | 1          | 11 |   |   | 1 | 1_ | 1_1 |  |

|---|---|---|---|---|----|---|-----|----|------|------------|----|---|---|---|----|-----|--|

|   | 1 | L |   |   | 1_ | 0 | 113 | Io | 01-1 | <u>t -</u> | 3  | 3 | 1 | L | L  |     |  |

|   |   |   |   |   |    |   |     |    |      |            |    |   |   |   |    |     |  |

In the above example:

:15.0\*-:3 will produce 491500000000 as the integer equivalent in standard UNIVAC excess 50 floating point format.

In all of the foregoing cases where items are connected by operators, if the value produced by an expression is a negative integer, it will be represented by a 2's complement unless the operation field of the line contains an EQU directive or, in some cases, the operation field is + or -.

### 5. Data Word Generation

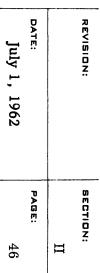

The UTMOST assembly system provides three means of generating data words other than expressions. These data words consist of Increment and Compare Words, two word constants, and words with a plus (+) or minus (-) operation field. The last category provides the ability to generate one word constants, indirect address words and field select words with or without index register indices.

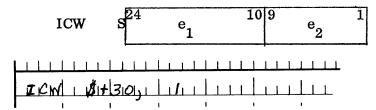

#### a. Increment and Compare WORD, ICW

The increment and compare word is used to prepare a word suitable for incrementing and comparing an index register (with the IX and IXC instructions).

The Increment and Compare word is written with ICW in the operation field of the line, followed in the operand field by two expressions,  $e_1$  and  $e_2$ . The first expression,  $e_1$ , represents the comparison amount and the second expression,  $e_2$ , represents the increment. The format of the generated word is illustrated below:

In the above example:

ICW informs the assembler that this is an increment and compare word. \$+30, the first expression, represents the comparison amount; 1, the second expression, represents the increment.

#### b. Two Word Constant Generation, TWC

A two word constant may be generated by placing TWC in the operation field of a line, and the constant in the operand field. This symbolic line must have a label. The assembler will generate the value of the expression in the operand field, right justify filling with binary zeros the resultant value in the two word field, and assign an address to the label. The left half

| REVISION:    | SECTION: |

|--------------|----------|

|              | п        |

| DATE:        | PAGE:    |

| July 1, 1962 | 19       |

of the two word constant may be addressed by using the label, the right half by using the label plus one.

| ZIEIRIO I ITIMCI I KIOIJI I I I I I |  |

|-------------------------------------|--|

|                                     |  |

| HIDIRI ITMIC I I(1 PIAKIE IMOI. 1)  |  |

|                                     |  |

In the above examples:

ZERO TWC (0) will produce a two word constant of binary zeros.

HDR TWC ('PAGE NO.') will generate a header line for editing purposes.

The first example may be referenced by ZERO+1 and a two register indicator in the "a" field of an instruction, the second by HDR+1, and a two register indicator in the "a" field.

- c. <u>+ or Operation Field</u>: A + or operation field plus from one to four expressions in the operand field may be used to generate specific constants consisting of a one word constant of datum, an indirect address word, a field select word without index register notation (or implied index notation), and a field select word with specific index register notation.

- One word data constants: One word constants may be generated by placing a + or a - in the operation field followed by one expression in the operand field. It is not necessary to leave a blank between the + or - sign in the operation field and the operand field.

| REVISION:    | SECTI |

|--------------|-------|

|              |       |

| DATE:        | PAGE: |

| July 1, 1962 |       |

20

П

| <del>A</del> 1 |                                 |

|----------------|---------------------------------|

|                |                                 |

|                | 1 HIVIALLUEIHIA 1 1 1 1 1 1 1 1 |

|                | H== 512180                      |

|                |                                 |

In the above examples:

- A will produce a one word alphabetic constant in six bit code containing the word "DATA".

- B will produce a one word constant containing the current value of the location counter in binary, right justified with preceding binary 0s and a negative sign.

- C will produce a positive binary constant containing the address plus ten of label "VALUE".

- D will contain a negative constant in excess three binary coded decimal notation preceded by binary zeros of the value "5280".

- 2) Indirect Address Words: Indirect address words may be generated through the use of a + or - operation field plus two expressions in the operand field. The first expression will be generated as a fifteen bit UNIVAC III address, and the second expression will be generated as a four bit index register code. The sign of the word will be the sign in the operation field.

HIDATIAH 1011 911 111

In the above example:

An indirect address word will be generated containing the fifteen bit address of the expression 'DATA+10' in the least significant fifteen bits of the word, Index Register #9 in the four most significant bits of the word, and the sign of the word will be positive, indicating that no chaining of indirect addresses is desired.

| REVISION:    | SECTION: |

|--------------|----------|

|              | п        |

| DATE:        | PAGE:    |

| July 1, 1962 | 21       |

3) Field Select Words: Field select words may be generated through the use of a + or - operation field plus three expressions in the operand field. The first expression will be generated into a five bit left bit control (plus binary three) integer indicating the left boundary of the field to be selected. The second expression will generate the right boundary of the field, also as a five bit binary integer plus binary three.

The third expression will generate a ten bit binary address for the word(s) from which the field is to be selected. The sign of the generated word must be positive.

| 1/21 | 1 <b>5</b> 11 | VIAILIK | EII |  |

|------|---------------|---------|-----|--|

|      |               | 1       |     |  |

In the above example:

The first expression will generate 01111 (binary 15) as the left bit control, the second will generate 01000 (binary 8) as the right bit control, and the ten bit address equivalent to 'VALUE' from the third expression.

4) Field Select Words: As in 3, above, a field select word may be generated using four expressions in the operand field following a + or - operation field. The first expression will generate the left bit parameter, the second expression the right bit parameter, the third expression the ten bit 'm' address, and the fourth will be used to generate the index register designator.

| ע און אואיאיאין איז |

|---------------------------------------------------------|

|                                                         |

In the above example:

The first expression will generate binary 15 as the left bit control, the second will generate binary 8 as the right bit control, the third will generate a ten bit address equivalent to 'VALUE', as modified by the index register, 8, specified in the fourth expression.

| UNIVAC III UTMOST | REVISION:    | SECTION: |

|-------------------|--------------|----------|

|                   |              | п        |

| UNITAC III UIMOSI | DATE:        | PAGE:    |

|                   | July 1, 1962 | 22       |

|                   |              |          |

#### 6. Mnemonic Instructions

The UTMOST assembly system utilizes a series of mnemonic instructions corresponding to the octal machine code instructions in object coding which are recognizable by the computer. The mnemonic operation codes describe the function of the instructions, thereby removing the problem of learning the octal operation codes, or their binary equivalents. In some cases, a combination of octal operation code and bits in the AR portion form instructions. Mnemonics have been created to save a programmer from writing or knowing the parameter AR bit configuration for most of these.

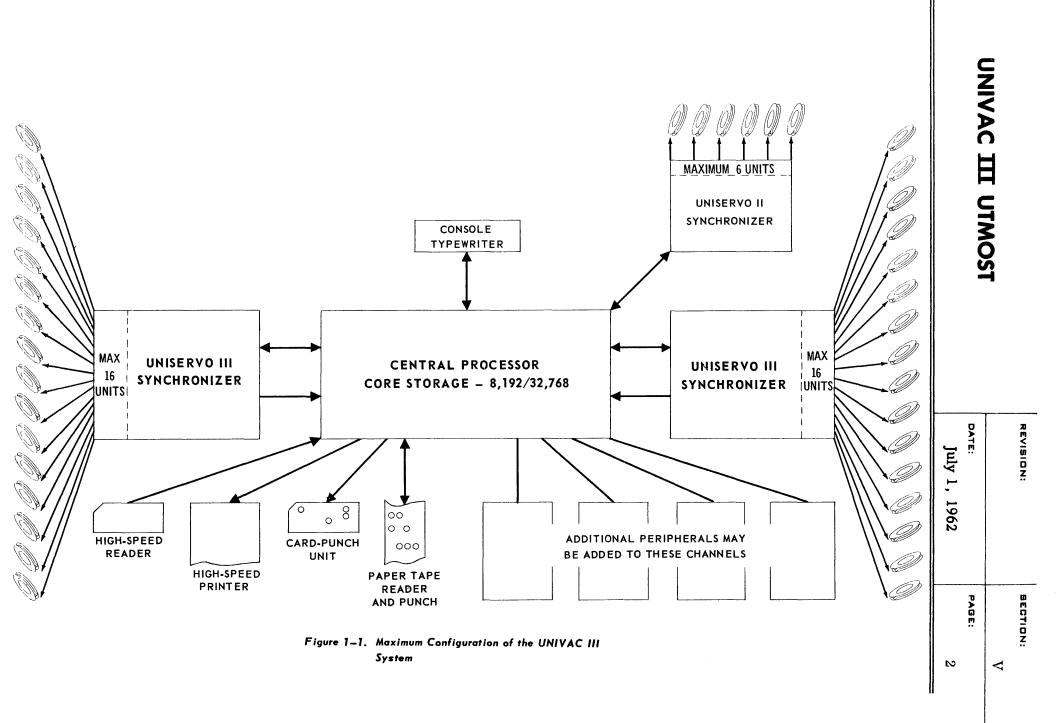

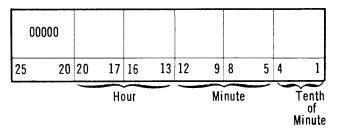

UNIVAC III's instruction word consists of a 24 bit word with the sign in bit 25 used to indicate either indirect addressing or field selection. The format of the word on a bit basis is illustrated below:

|   | 24 | 21 | 20 15 | 14 11 | 10 1 |

|---|----|----|-------|-------|------|

| s | b  |    | ор    | a     | m    |

where "b" indicates the index register designator,

"op" the operation code,

"a" the arithmetic register(s) designator, and

"m" the ten bit area address of the operand.

Since UTMOST provides semi-automatic insertion of area index register assignments, it is unnecessary to write a "b" designator in many cases.

(USE Directive) The order of writing a symbolic instruction line has been altered from the hardware format to provide greater convenience in programming. The format is:

| UNIVA | СШ | UTM | OST |

|-------|----|-----|-----|

|-------|----|-----|-----|

| REVISION:    | SECTION: |

|--------------|----------|

|              | <u> </u> |

| DATE:        | PAGE:    |

| July 1, 1962 | 23       |

Type 0 Instructions: Type 0 instructions have three fields representing the "a", "m", and "b" fields of the instruction word, respectively. The sign of the instruction will be + unless the "m" portion of the instruction is preceded by an asterisk indicating indirect addressing or field selection.

| ALLA LIL      | 161.01        | $\sum_{i=1}^{n}$ |                   |     |

|---------------|---------------|------------------|-------------------|-----|

| JOIRI   11,1  | ITIEIM PITIGI |                  |                   | 111 |

| I I ISTAI I I |               |                  |                   |     |

|               | -9-17         | <u>aj 171</u>    | - <u>I. I. I.</u> |     |

In the above illustration:

LA, OR, and SA are mnemonic instruction codes of type 0 category, requiring in each case the "a", "m", and "b" fields. (The "b" field may be omitted, if the USE assembler directive has been inserted in the program prior to the assembly encountering these instructions.

Type 1 Instructions: Type 1 instructions have two fields representing the "m" and "b" portions of the instruction word, respectively. The sign of the instruction word will be + unless the "m" portion of the instruction is preceded by an asterisk indicating indirect addressing or field selection.

| JIEWDI, 1111                              |  |  |  |

|-------------------------------------------|--|--|--|

|                                           |  |  |  |

| JI 1* AIRIRIA NIGIEI-11,114 1111111111111 |  |  |  |

In the above illustration:

J is the mnemonic code for the Jump instructions, the first instruction utilizing direct addressing, the second indirect addressing.

### 7. Line Item

A line item is an instruction line, form reference line, or data word line without label field and without leading or trailing blanks, enclosed in parentheses.

121A1 24,112 (MIAISIK 171017/017101701)11111

| UNIVAC III UTMOST | <b>PAGE:</b> |

|-------------------|--------------|

| July 1, 1962      | 24           |

In the above examples:

- LA 1, (J \$+5) The last expression is an instruction line written as line item.

- LA 2, (MASK 70707070) The parenthetical expression (MASK 70707070) is a form reference line written as a line item.

- LA 4 ('DON') The parenthetical expression ('DON') is a data word line written as a line item.

In each case, the assembler will generate an address which will be the address of the translated parenthetical expression. The translated parenthetical expression is called a literal. If the literal is identical to any other literal, the location assigned is the location of the previous literal, thus eliminating duplication.

When a line item appears in the address field of an IX or IXC instruction and has two expressions, it is evaluated as a data word with ICW in the operation field.

In the above example:

The assembler will generate an index register increment and compare word equivalent to the same expressions in an ICW line.

A literal will be double precision if the line was a TWC line or if it was a data line with one expression and the mode of the expression was floating.

| LA   |      | LITIMC | 1)PIA | GEII |  |

|------|------|--------|-------|------|--|

|      |      |        |       |      |  |

| ILAI | 1121 | 1131-  | JI4DI |      |  |

In the above examples:

The first example will generate a two word constant (double precision) of the alphabetic constant "PAGE NO."

The second example will generate a two word excess 50 floating point constant where 3.14 is equivalent to 513140000000.

| UNIVAC | Ш | UTMOST |

|--------|---|--------|

|--------|---|--------|

### 8. Assembler Directives

The UTMOST assembler provides the programmer with a series of powerful operation codes in the form of Assembler Directives. These assembler directives do not produce coding in and of themselves, but effectively provide a programmed means of controlling the process of assembly.

There are ten assembler directives as shown in the table below:

|     | Directive | Purpose                                     |

|-----|-----------|---------------------------------------------|

| 1.  | EQU       | Equate operand value to label field.        |

| 2.  | RES       | Reserve memory locations.                   |

| 3.  | USE       | Assign index registers for area addressing. |

| 4.  | FORM      | Designate arbitrary word format.            |

| 5.  | FLD       | Specify Field Selection pattern.            |

| 6.  | END       | Designate end of program or procedure.      |

| 7.  | DO        | Generate designated line(s) of coding.      |

| 8.  | PROC      | Generate associated coding if referenced.   |

| 9.  | NAME      | Qualify procedural coding.                  |

| 10. | SET       | Set index register to assumed value.        |

None of the assembler directives except RES will cause the location counter to be incremented. However, if coding is generated as a result of an assembler directive, the location counter will be incremented in the usual manner. A detailed discussion of each directive follows in this section.

| REVISION:    | SECTION: |

|--------------|----------|

|              | II       |

| DATE:        | PAGE:    |

| July 1, 1962 | 26       |

### a. EQU

The EQU assembler directive causes the label in the label field of its line to be equated in all succeeding references in the coding to the value of the expression in the operand field of the symbolic line. Thereafter, the label may be used in an expression, and the assembler will substitute for the label the integer value of the original expression in the operand field of the EQU line.

| ┠┙╹╘╘╘┺╧       |        |                   |  |

|----------------|--------|-------------------|--|

| PIRILI EIGIUL  | 181    |                   |  |

| AIRIZI EKSILLI |        |                   |  |

| AIRIBI EIQIUI  | 21     | 1                 |  |

| AIRI4I EIQILLI |        |                   |  |

|                | ······ | · · · · · · · · · |  |

In the above example:

The four arithmetic register names have been equated to the binary values utilized in object code to address the respective registers. After these four EQU directives have been encountered by the assembler, the AR portion of an instruction may contain the label names of the registers, and the assembler will recognize them as the associated binary values. Accordingly, coding referencing these registers could read as follows:

| I ILAI                                        | ARILHARIS    |   |

|-----------------------------------------------|--------------|---|

|                                               | ARIZI+IARI41 |   |

|                                               | ARTITIA      |   |

| , <u>, , , , , , , , , , , , , , , , , , </u> | · · · ·      | . |

b. RES

The RES assembler directive causes the value of the expression in the operand field to be added to the location counter. It may be used to reserve a specific or variable number of locations for input/output storage, or any other programmable purpose. (If the expression in the operand field is negative, the value of the expression will effectively be deducted from the location counter.) If it is desired to address any location within a reserved area, the label associated with the reserve directive may be used.

| REVISION:    | BECTION: |

|--------------|----------|

|              | п        |

| DATE:        | PAGE:    |

| July 1, 1962 | 27       |

In the above example:

The RES directive will cause 32 words of storage to be set aside (32 will be added to the location counter). These 32 words are equivalent to the 32 words or 128 characters required for one line on the High Speed Printer.

| 1 |                                                    |

|---|----------------------------------------------------|

|   | ILIAI AIRIJI + AIRIZI, PIRINITAIRIEIA + 151 111    |

|   | ISTAL AIRUITAIRIZI, IPIRINTIAIRIZTAITIZII IIIIIIII |

The two symbolic lines reference words 15 and 16, and 31 and 32 in the reserved area respectively.

c. USE

The USE assembler directive is utilized to load index registers with base values relative to the value contained in the location counter at the time the USE directive is encountered by the assembler. After a USE directive is encountered, it is not necessary to indicate index register designators in the operand field of a symbolic instruction line, since the assembler will insert the values automatically, unless a specific index register is desired by the programmer.

The USE directive, when encountered by the assembler will assign the current value of the location counter to the first index register specified in the operand field of the USE line, the current value plus 1024 to the second, and so on through the number of index registers specified in the operand field of the line.

It is possible to use more than one USE directive in a program, however, the value assigned an index register by a USE directive is loaded into that register at object time. Therefore, any particular index register may not be referred to more than one in a USE directive, or series of USE directives.

|                   | REVISION:    | SECTION: |

|-------------------|--------------|----------|

| UNIVAC III UTMOST |              | п        |

| UNIVAC III UIMOSI | DATE:        | PAGE:    |

|                   | July 1, 1962 | 28       |

|                   |              |          |

In the above example:

Assuming that the location counter reads 4000 at the time the directive is encountered, IR 5 will contain the value 4000, IR 6 will contain 5024, and IR 7 will contain 6048. IR's 5, 6, and 7 will automatically be inserted into object code where required by the program, and no indexing has been specified by the symbolic coding.

d. FORM

The FORM assembler directive may be used to define arbitrary word formats, label these formats, and thereafter reference the format by using the associated format label as an operation code in the operation field. When the assembler encounters a FORM directive, it notes the pattern specified in the operand field. Thereafter, the expressions in the operand field of the associated label, appearing as an operation code, will be interpreted and generated in the "form" specified by the initial directive.

In writing a FORM directive, the label field must contain a label, the operation field must contain the directive FORM, and the operand field must contain a series of expressions whose sum is equal to 25, the total number of bits in a UNIVAC III word (a single expression = 25 is illegal)

|        | REVISION:    | SECTION: |

|--------|--------------|----------|

| UTMOST |              | п        |

|        | DATE:        | PAGE:    |

|        | July 1, 1962 | 29       |

| ZINISIT FORMI 1 11,141,161,141, 10111111          |  |

|---------------------------------------------------|--|

|                                                   |  |

| III IIMBIT III dy 5 1 1911 1311 1311 1011 1400 11 |  |

|                                                   |  |

In the above example:

UNIVAC III

The FORM directive has been used to define an object code format equivalent to a UNIVAC III instruction word. When INST is encountered by the assembler in the operation field of a symbolic line, the expressions in the operand field will be generated into a sign bit, 4 bit "b" field, 6 bit "op" field, 4 bit "a" field, and a 10 bit "m" field.

| 4 | M. | AL S | 3IK  | 1 | F | b  | N R | M | 1        |   | 1  | فل را | <u>3</u> 1, | 3        | ا را | <b>≩</b> 1, | 13         | ١, | 3  | <u>l</u> , | 3  | ارا | 3  | цĻ | 3 | L | 1 |

|---|----|------|------|---|---|----|-----|---|----------|---|----|-------|-------------|----------|------|-------------|------------|----|----|------------|----|-----|----|----|---|---|---|

|   |    |      |      |   |   |    |     |   |          |   |    |       |             |          | Ĺ    |             |            |    |    |            |    |     |    |    |   |   |   |

|   |    | ŕ    | 1  A | 3 | Ŕ | 1_ | 1   |   | <u> </u> | 0 | را | a     | -19         | <u>,</u> | رما  | <u> </u>    | <u>2</u> , | 0  | J, | 0          | 4, | 0   | L, | IZ |   | 1 | _ |

| I | ł  | I    | I    |   | I | I  | ŀ   |   | ł        |   |    |       | 1           |          |      | 1           | 1          |    | 1  | L          | Ĺ  |     | L  | Ц  |   | 1 | _ |

In the above example:

r

The FORM directive has been used to provide a simple means of writing a masking constant in octal mode equivalent to a UNIVAC III word. Whenever the label MASK appears in the operation field, the assembler will generate the appropriate masking constant. As illustrated in the second line above, the use of MASK in the operation field followed by the expressions 0, 0, 0, 7, 0, 0, 0, 0, 7 will generate a masking constant in the following pattern: + 000 000 111 000 000 000 0111.

| REVISION:    | SECTION: |

|--------------|----------|

|              | 11       |

| DATE:        | PAGE:    |

| July 1, 1962 | 30       |

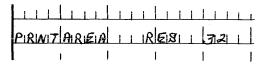

In the above example:

The FORM directive has been used to define a printer control word. The first example below the form directive will generate a line of object code which will cause the paper to be spaced 5 lines, and printing to take place from location 1004 through location 1035. The second example will cause the paper to be spaced 2 lines. The third example will cause the generation of a line which will cause the paper to be spaced 6 lines, and printing to take place from location 13254 through location 13285. In all cases interrupt is specified.

3. <u>SET</u>

The SET assembler directive may be used to arbitrarily indicate to the assembler that a specific value should be assigned to an index register for assembly purposes. The value assigned will be utilized by the assembler for automatic index register assignment until another SET directive specifying the same index register is encountered by the assembler. The assembler does not load the index register, that is the responsibility of the programmer. The format of a SET directive consists of SET in the operation field followed by two expressions. The first expression indicates the index register to be set, the second expression indicates the value to which the register is to be set.

| 11/4/11/5,  | <b>K</b> |

|-------------|----------|

| GF+ LIF     |          |

| 111 BET 115 |          |

In the above example:

Index Register 15 will be assumed by the assembler to contain the integer value equivalent to the current content of the location counter. The index register load instruction immediately preceding physically will accomplish the actual loading of IR 15 with the value of \$.

| REVISION:    | SECTION: |

|--------------|----------|

|              | п        |

| DATE:        | PAGE:    |

| July 1, 1962 | 31       |

#### f. FLD

The FLD assembler directive may be used to define the leftmost and rightmost bit limits of a field. A FLD directive line must have a label in the label field, FLD in the operation field, and the operand field must contain two expressions defining the left and right bit boundaries of the field. After a FLD directive has defined a field, the label may be used followed by the label in parentheses of the word(s) containing the field.

| LANT L | FIMD I LIE |                     |

|--------|------------|---------------------|

|        | +          |                     |

| 114    | ALABILI    | LILMITI (IVIAILIUE) |

In the above example:

The label LMT has been defined as a field label through the use of the FLD directive. Its leftmost bit is bit 12, its rightmost bit is bit 1.

In the symbolic coding following, AR1 is being loaded from word VALUE as defined by the field LMT; i.e., bits 1-12 of word VALUE are being loaded into AR1.

g. END

The END assembler directive indicates to the UTMOST assembler that the last line of symbolic code in a program or procedure (PROC assembler directive) has been read by the assembler. This directive is required both at the end of a program and of a procedure. In the case of a procedure, the operand field is ignored by the assembler. In the case of a program, the starting address of the program should be placed in the operand field in the form of an expression.

| REVISION:    | SECTION: |

|--------------|----------|

|              | п        |

| DATE:        | PAGE:    |

| July 1, 1962 | 32       |

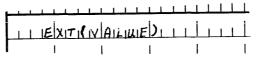

| J. WEXT |                        |

|---------|------------------------|

| LIEND   | STIRTT. EWD OF PROGRAM |

In the above example:

END indicates that the last line of coding in the program has preceded the END directive. The label STRT will be the starting address of the assembled program.

| END END OF PROCEDURE: OAERAND |

|-------------------------------|

| FILELID IIS IIGNIORED         |

|                               |

In the above example:

END indicates that the last line of coding of a procedure has been read. The content of the operand field of a procedural END directive is ignored.

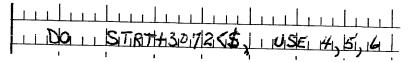

h. DO

The DO assembler directive may be used to optionally generate a line of coding a variable number of times. A DO symbolic line consists of an optional label, DO in the operation field, an expression in the operand field stating the number of times the DO is to be performed, and any symbolic line.

The format of a DO assembler directive is:

label DO e<sub>1</sub>, line.

The label associated with a DO directive varies from the usual type of label in that, when referenced, its integer value will be equal to the number of times that the DO directive has been performed.

| REVISION:    | SECTION: |

|--------------|----------|

|              | п        |

| DATE:        | PAGE:    |

| July 1, 1962 | 33       |

The expression of a DO directive,  $e_1$ , is a value which indicates to the assembler the number of times the associated line is to be generated. The 'line' may be any legitimate symbolic line of coding, or any directive except EQU, FORM, PROC, NAME, and END.

In the above example:

If the current value of the location counter is greater than the initial value of the location counter plus 3072 (3x1024), a 1 will be generated by the = operator. In that case, the assembler will be controlled by the USE directive line in the DO symbolic line, and three additional index registers will be set up by the assembler. If the condition is not met, a 0 will be generated, and the USE line will not become effective.

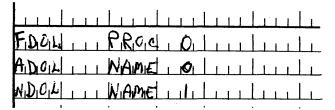

#### i. PROC

A PROC assembler directive informs the assembler that all succeeding symbolic lines until an END directive is read, are not to be assembled, but retained by the assembler until referenced by some other portion of the symbolic program. When the PROC (procedure) is referenced, the symbolic coding associated with the PROC will then be assembled and inserted into the object program.

A PROC directive line must have a label and the expression in the operand field indicates the maximum number of lists of expressions associated with the procedure, if any.\* If no expression is given, the number of lists is indeterminate. (No expression is indicated by a period followed by a blank. In this case, every reference to the PROC must have a period followed by a blank following the last line.)

A discussion of PROC lists follows under the NAME directive.

| REVISION:    | SECTION: |

|--------------|----------|

|              | п        |

| DATE:        | PAGE:    |

| July 1, 1962 | 34       |

| TRIAN PROCLOS                            |

|------------------------------------------|

| LILLIA LIBIS BUILING                     |

| 111 SA 115 10 19111                      |

| 111 JIV JK 1 18 1 14 11 111              |

| ++++++++++++++++++++++++++++++++++++++   |

| III EMD IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII |

|                                          |

In the above example:

The PROC line has the label TRAN (for TRANsfer), PROC in the operation field and a 0 in the operand field indicating that there are no lists associated with the PROC. The four lines of coding following make up a very simple straight line four word transfer routine followed by an END directive.

The previous procedure may be referenced by the following symbolic coding:

| LILLAX BIN K (RESERVED) |  |

|-------------------------|--|

| LIX 1911 HOURIENTDI     |  |

| II DG BIN TRAN III      |  |

|                         |  |

The DO directive line will cause the procedure to be generated five times, since the expression in the DO line is 5, effectively generating the following symbolic coding transferring twenty words.

.....

|          | REVISIO      | אנ:       | SECTION: |   |

|----------|--------------|-----------|----------|---|

|          |              |           | I        |   |

|          | date:<br>Jul | y 1, 1962 | PAGE:    | 5 |

| PERATION | Δ            | OPERAND   |          |   |

| 1 LABEL   | ∆ OP                 | ERATION        | Δ       | OPERAND |

|-----------|----------------------|----------------|---------|---------|

| LA        | 15                   | OLI BI         |         |         |

| III SIAI  | 151                  | 101,1 1911     |         |         |

| TXI       | 181                  | (4). I         | 1 1 1   |         |

|           | <u>  9</u> ]         | <u> </u>       |         |         |

| II LAL    | 15,                  | 0,18,          |         |         |

| II BAI    | 1/51                 | 0,19,1         | 1 1 1 1 |         |

|           | $    \partial_{ij} $ | -1-(4)         |         |         |

| III TIXI  | 191                  |                |         |         |

| LILALI    | ارْك/ال              | PU BU          |         |         |

| II SAL    | 1151                 | 011 911        |         |         |

| IIIIXII   | 181                  |                | 1 1 1 1 |         |

|           | 191                  | 1(4)           |         |         |

| LI KAL    | $\perp j \leq 1$     | a, B           |         |         |

| II SAI    | اراكلا               | <u>_Qj 9</u> _ |         |         |

|           | Bi                   | (4)            |         |         |