# PROGRAMMING FOR THE UNIVAC FAC-TRONIC SYSTEM

January 1953

COPYRIGHT 1953 BY REMINGTON RAND INC. ECKERT-MAUCHLY DIVISION PRICE \$18.50

## PREFACE

A solution to a mathematical or industrial problem resulting from an application of the UNIVAC Fac-tronic System is evolved through four broad stages, namely:

- (1) Problem analysis

- (2) Programming or encoding

- (3) Running the problem on the computer

- (4) Interpretation and proper use of results

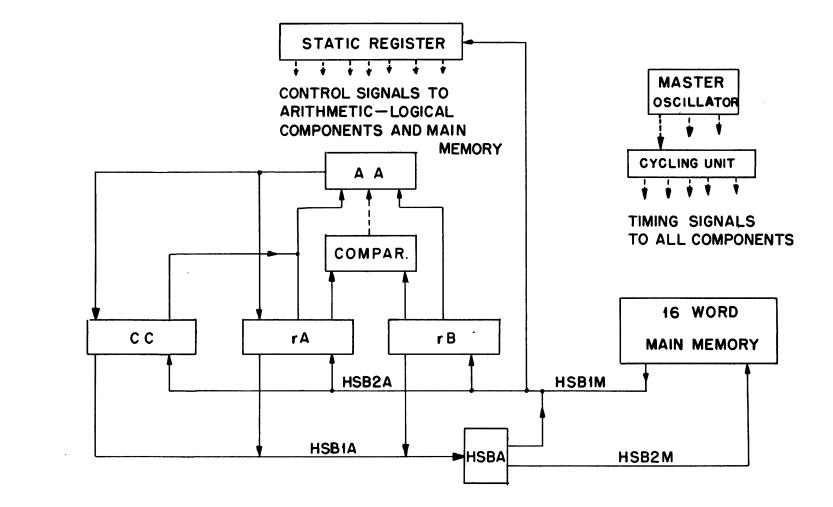

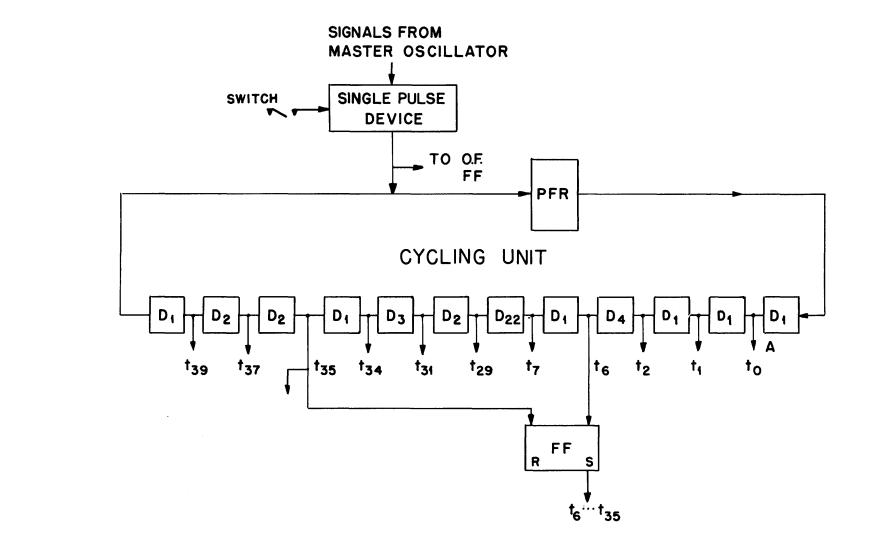

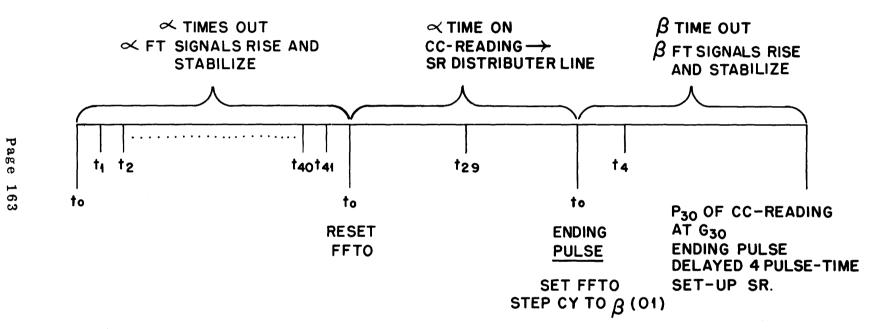

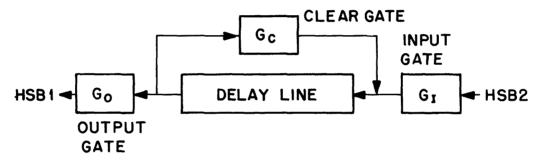

This manual is primarily concerned with the processes of programming and such other concepts which are necessary to a coordinated study of this subject. Hence, the chapters which follow will include some references to analysis, planning and actual computer operation.

Although the material herein presented is basic and complete, it should be clear that this manual is not intended to be a comprehensive study of the subject. It should be especially evident that no attempt has been made to include a discussion of electronics which would lead to an understanding of the design of UNIVAC and to an understanding of a complete logical functioning of its component parts. However, for those who are interested in, and prepared to comprehend the fundamental operation of UNIVAC, Chapter 9 offers opportunity for an elementary understanding of these con-Chapter 9 is independent of the other chapters of cepts. the Manual and may be read concurrently with them. It is planned that a later treatise, Manual 2, will develop these notions further and will also include many of the more advanced techniques of programming and analysis essential to the student requiring a total understanding of the subject.

This text is a first revision of the Programming Manual dated March 23, 1951, and an attempt has been made to construct, as nearly as possible, a self-study treatise. To this end a number of accepted pedagogical techniques have been introduced. For example, many well graded illustrative problems will be found throughout the text followed by practice exercises for the reader. In addition, some review practice exercises are included in the Appendix. The device of providing abundant repetition of basic concepts has been deliberate in an attempt to foster good learning. The preliminary discussions found in the first sections of most chapters will serve to coordinate the material in previous chapters with current developments.

Particular emphasis has been placed in the instructions to the UNIVAC. In addition to "blocking in" these instructions for emphasis, they are

- (1) discussed in the body of the text

- (2) assembled and repeated in the Appendix with additional pertinent information.

- (3) summarized on one page and located, for convenience, in a pocket in the back of the manual.

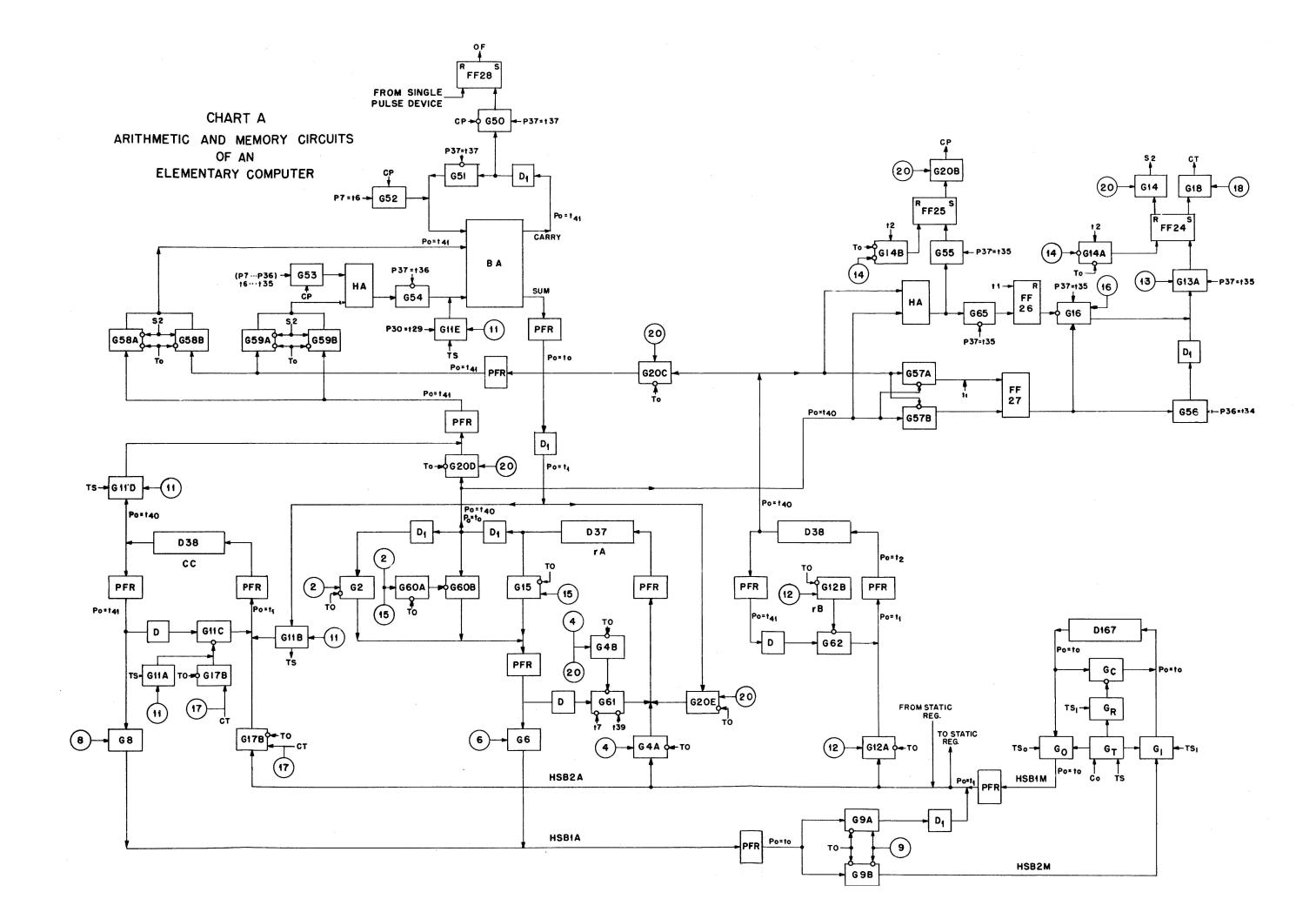

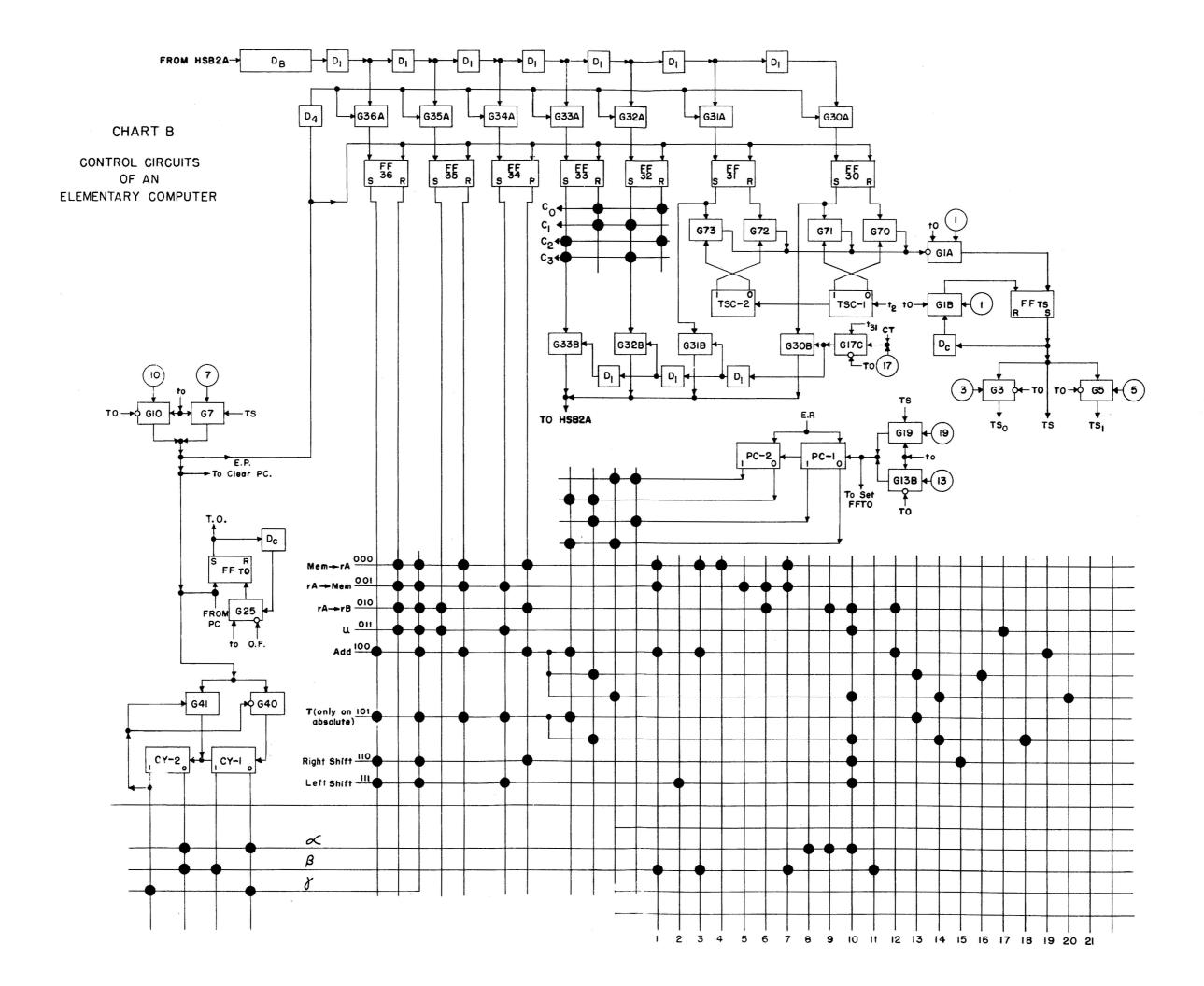

Finally, two charts will also be found in the pocket located in the back of the manual. These charts are to be used in connection with the discussion of Chapter 9 and it will be useful to follow the descriptions in this chapter with the "loose" charts available for reference.

January 1953

## Programming for the UNIVAC FAC-TRONIC SYSTEM

## CONTENTS

| Chapter |                                                          | Page |

|---------|----------------------------------------------------------|------|

| 1       | Introduction to the UNIVAC FAC-TRONIC SYSTEM             | 1    |

| 2       | Representation of Information                            | 15   |

| 3       | Registers                                                | 28   |

| 4       | Fundamental Arithmetic Operations                        | 39   |

| 5       | Arrangement of Information                               | 57   |

| 6       | Transfer of Control                                      | 71   |

| 7       | Overflow                                                 | 83   |

| 8       | Input, Output                                            | 96   |

| 9       | Elementary Description of the<br>Operation of a Computer | 115  |

| 10      | Flow Charts - An Aid to Programming                      | 176  |

| 11      | Appendix                                                 | 221  |

|         | Index                                                    | 245  |

# Chapter I

# Introduction to the UNIVAC Fac-tronic System

Section

Topic

## Page

| 1 | Historical Development                    | 1  |

|---|-------------------------------------------|----|

| 2 | Component Parts of UNIVAC                 | 5  |

| 3 | Some Applications of the<br>UNIVAC System | 10 |

| 4 | Responsibilities of the Pro-<br>grammer   | 12 |

## SEC. I. HISTORICAL DEVELOPMENT

Around the clock, day after day, UNIVAC Fac-tronic Systems are now being used to process information and carry out billions of complex operations. New standards of reliability and accuracy have been set by the self-checking UNIVAC equipment, and users have confirmed that their overall costs for obtaining these dependable results are significantly lower than those which would have been incurred by use of alternative devices. The UNIVAC Systems already in operation have been tried out on an increasing variety of problems, demonstrating anew for each different problem that the equipment deserves the name, Universal Automatic Computer, from which the word UNIVAC was formed. Examples range from the most complicated mathematical equations to systems of accounting and inventory control, with automatic writing of purchase orders when stocks are low. As a comprehensive tool, its ability to handle and process information efficiently and at low cost can be demonstrated both for involved scientific calculations and for all of the manifold tasks which any large business enterprise finds necessary to its operation and administration.

As the application of the UNIVAC System to all of these diverse problems continues to grow, the need for personnel trained in the use of computers grows rapidly. Large business organizations have long had methods departments or specialists in business systems whose task it was to survey their operations and investigate possible improvements. The advent of the UNIVAC System has now created a new profession. that of translating the analysis of a business system into a practical scheme for automatically producing the desired results from the available raw input information. This significant development has its counterpart in the Scientific world as well. A new kind of mathematics is being born; no longer are we content with crude approximations which were once accepted because "the more exact equations are too difficult to solve". Both design engineers and theoretical physicists are finding ways to compute the numbers they want to the accuracy they want, and in doing so they are building a new kind of mathematics--which will ultimately have as profound an influence on the Queen of the Sciences as did the

Page 1

### invention of the calculus.

This programming manual is but a first step toward making available the basic information needed by those who wish to learn how to control the UNIVAC System and make it do their This manual is concerned only with the nature and bidding. use of the UNIVAC Instruction Code and the general method of using "flow charts" to symbolize and analyze any systematic sequence of operations. The examples have been chosen to illustrate common techniques. This is an introduction, not an exhaustive treatise or complete handbook. Although this manual has already been revised several times, it is to be expected that some readers will be able to suggest other modes of presentation which they believe more effective. It is hoped that we may have the benefit of such suggestions for the improvement of future editions.

Before describing the main components of the UNIVAC System, the historical background of computer development will be sketched. Over one hundred years ago Charles Babbage, an English mathematician, worked hard and long over his "computing engine" which, using mechanical parts, embodied all of the versatility and generality to make it a truly general purpose computer. His ideas were excellent, but the materials and techniques available in his day were not suited to the translation of his ideas into an operating mechanism. Even had the mechanism been possible, it would not have been able to justify its cost, for its operating rate would have been slow.

Babbage's invention was forgotten until Professor Howard Aiken at Harvard University designed Mark I, the first largescale automatic computer ever to be put in operation. This device, first put in operation in 1944 was constructed by I.B.M. using many of their standard punched card electromagnetic components. It has been operated 364 days per year ever since. Subsequently, Professor Aiken designed and built Mark II and Mark III for the Naval Ordnance Proving Ground at Dahlgren, Virginia, where these two machines are now operating. Mark II uses relays, and punched paper tapes; Mark III has a large storage capacity magnetic drums, electronic and magnetic arithmetic circuits, and paper magnetic tape for inputoutput. Mark I and Mark II contain no electronic circuits, but vacuum tubes were used in Mark III.

The development of <u>electronic</u> large-scale computers has a guite separate and independent history. In attempting to carry out statistical calculations on large volumes of weather data, Dr. John W. Mauchly became convinced that the ultimate solution would be to adapt electronic techniques to high-speed automatic computation. His initial experiments in this direction were on a small scale, but in 1943, the war-time requirements of Army Ordnance brought about a computer development contract between the Government and the University of Pennsylvania, based on a 1942 proposal by Dr. Mauchly. At this time. Mr. J. Presper Eckert, Jr. became Chief Project Engineer, and he and Dr. Mauchly together outlined a generalpurpose high-speed digital computer which (except for inputoutput facilities) was entirely electronic. This computer. completed in December 1945 and announced early in 1946, was known as the ENIAC (Electronic Numerical Integrator and Computer). With a staff of only 12 engineers assisting them, Dr. Mauchly and Mr. Eckert were able in the short span of two and one-half years to convert their pencil-and-paper ideas into a working ensemble of almost 20,000 vacuum tubes. The ENIAC, subsequently moved to Aberdeen Proving Ground, is today operating around the clock with high efficiency and dependability.

Before the completion of the ENIAC, Dr. Mauchly and Mr. Eckert were ready with plans for a more powerful computer which, by the use of newly invented principles, could be made with far fewer tubes. Their plans were described in a classified report to Army Ordnance in September 1945, by which time the new design was known as the EDVAC (Electronic Discrete Variable Computer). Characteristic of the new design was the use of sound waves in tubes of mercury for the storage of large numbers of digits in immediate readiness for computer use. A further innovation was the decision to store all computer control instructions in these same mercury tanks, so that operations on the instructions were just as easy as operations on the data. The use of magnetic tapes for reading in the instructions and data, and for recording intermediate or final results, was also proposed.

At that time, digital recording on magnetic tapes was a novelty, and even the now-familiar recording of sound on magnetic tapes was in its infancy. One further major difference between the EDVAC and the ENIAC may be noted: ENIAC did many operations in parallel, while EDVAC was to be strictly a serial computer, doing only one operation at a time, but achieving its speed by stepping up the basic "pulse rate" from 100,000 per second in the ENIAC to at least one million per second in the EDVAC.

In 1946, Mr. Eckert and Dr. Mauchly resigned from the University and set up their own company, which began as a partnership under the name "Electronic Control Company". With a staff of only a few engineers they began, under contract with the National Bureau of Standards, to develop the components and logical plans for an electronic computer which would handle alphabetic as well as numeric data, and which would have a versatility and flexibility far beyond that usually implied by the term "computer". Although perfection of the mercury tank method of storing information was by no means easy, probably the most difficult but at the same time most necessary development effort was that required to achieve a workable and dependable high-speed magnetic tape unit for input-output use. Their success in so doing is now a matter of record, and the ready access which the UNIVAC System provides to an exceedingly large amount of information on tape is an important factor contributing to the versatile performance of that system.

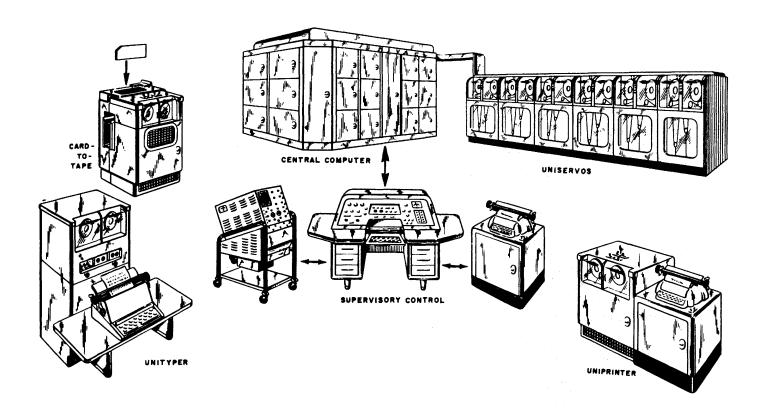

The name "UNIVAC" refers to an assemblage of equipment which includes a computing unit and several auxiliary devices to provide a communication train between the computer and the human inquirer. Information is represented in the central computer by a train of electrical or acoustic pulses. Three auxiliary devices, UNITYPER, UNISERVOS, and UNIPRINTER are used to translate information between the printed page and the computer's language medium. Chapter 1

The <u>UNITYPER</u>, which contains a keyboard similar to a typewriter keyboard, converts data to apredetermined pattern of pulses impressed on magnetic tape. Each keystroke records the pulse pattern corresponding to that character on magnetic tape. Typing errors which the typist has sensed can be corrected by backspacing and retyping. The tape is automatically erased as new information is impressed over the erroneous characters.

The UNISERVOs contain magnetic reading and recording heads and a mechanism to manipulate the tapes. The UNISERVOS are controlled by the Central Computer. A read instruction directs the proper UNISERVO to connect its magnetic head to the read circuits and to move the tape past the magnetic Each pulse recorded on the magnetic tape generates an head. electrical pulse in the read circuits as the tape sweeps by the magnetic head. The information which was recorded on tape as a pattern of pulses appears in the read circuits as a train of electrical pulses corresponding to the pattern of pulses on the tape. The train of electrical pulses is delivered to an auxiliary memory in the input circuits without delaying the Central Computer. When desired, the data is transferred from the input storage to the high-speed memory. Information can be read from tape in either the forward or backward direction.

A write instruction directs the proper UNISERVO to connect its write circuit to the recording head and to move the tape past the recording head. The tape is automatically erased before any information is recorded on it. A train of electrical pulses representing the information to be written is delivered to an auxiliary memory in the output circuits, and as the Central Computer continues computation, the information is delivered to the write circuits of the UNISERVO from the output circuits of the Central Computer. A magnetic pulse is impressed on the tape whenever an electrical pulse appears in the write circuits. Information is written on tape in only the forward direction. The <u>UNIPRINTER</u> translates information recorded on tape into a typewritten copy. The UNIPRINTER contains a standard electric typewriter. The typewriter keys are actuated in accordance with the pulse patterns on the tape. All keys, including upper and lower cases of the alphabet, punctuation marks, spaces, tabs, and carriage returns operate automatically. However, margin and tab stops are set by hand. A tape "edited" by the Central Computer for printing is complete in all details. Both the UNITYPER and the UNIPRINTER operate independently of the Central Computer.

Since much information is already recorded in punchcard files, a <u>Card-to-Tape Converter</u> has been designed. This device reads the holes photo-electrically and converts the information into pulse patterns on magnetic tape.

The tape is metallic and will not corrode. It is plated with a magnetic material. Information recorded on it may be stored permanently. A tape may be erased and reused when the information stored on it is of no further value. The tape is a few thousandths of an inch thick, one half inch wide, and of high tensile strength. Unityped tapes and tapes prepared by UNIVAC for printing on the UNIPRINTER are transcribed at a density of twenty characters to the inch. Tapes prepared by the Card-to-Tape Converter and tapes prepared by the Central Computer to be reused in computer operations are transcribed at a density of one hundred characters to the One reel of tape, eight inches in diameter, contains inch. approximately 1,500,000 characters at adensity of one hundred to the inch.

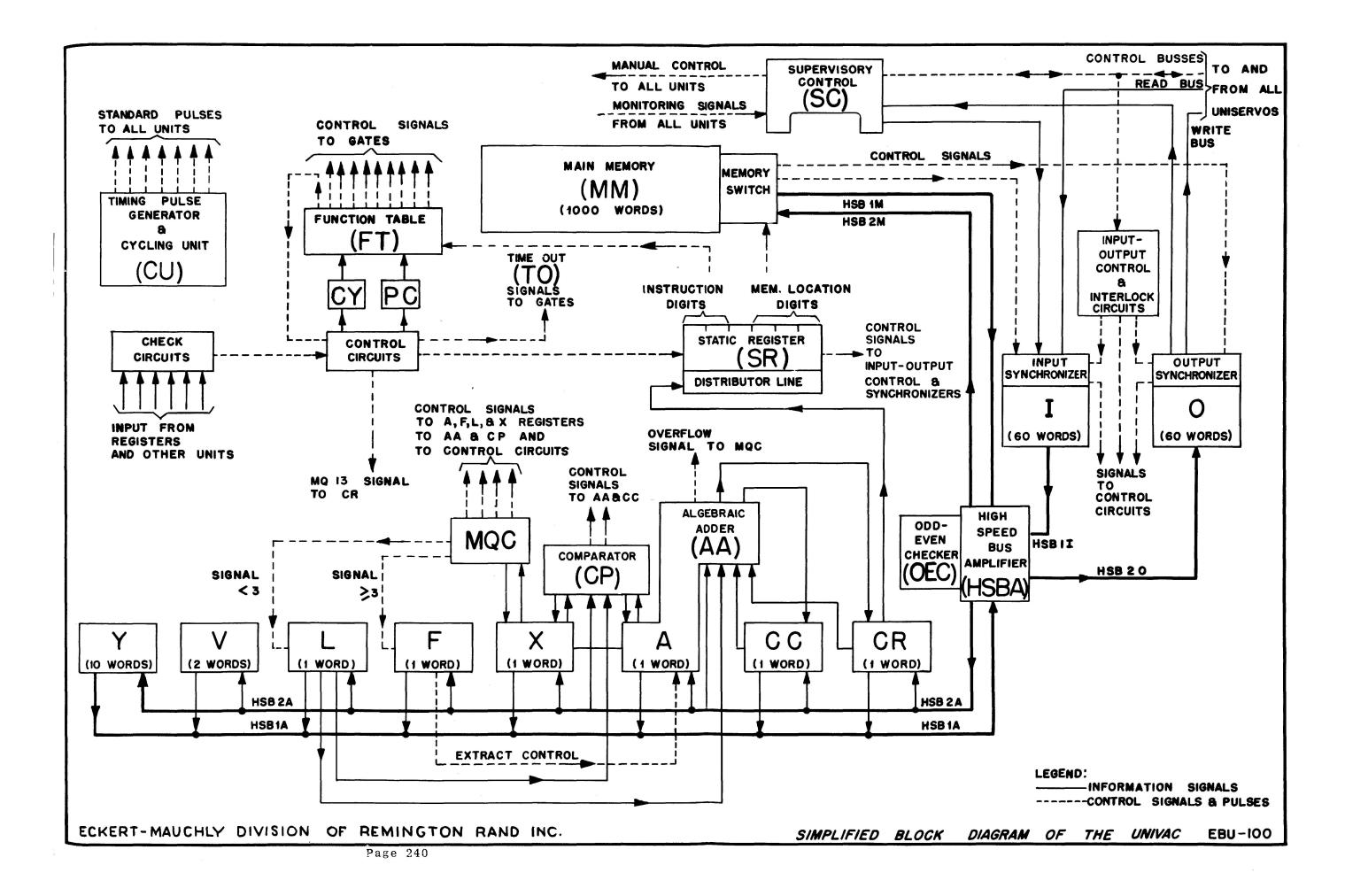

The <u>CENTRAL COMPUTER</u>, the core of the UNIVAC System, performs the logical and arithmetic operations necessary to the solution of a problem. The Central Computer contains input and output circuits, a memory, arithmetic and logical circuits, and circuits to control the sequence of operations. The tape drives of the UNISERVOS are not synchronized with the internal operating circuits of the Central Computer. Information read from tape is received in the input circuits and auxiliary memory in readiness for the operations which are to be performed. Results are stored in the memory as they are produced and are delivered to the auxiliary memory in the output circuits when they are to be recorded on tape.

The arithmetic and logical circuits perform basic operations at high speed. Essentially, these operations may be reduced to addition, subtraction, multiplication, division, comparison, and the selection and assemblage of data.

The control circuits link the instructions and the arithmetic units. They automatically sequence the operations of the computer as directed by the instructions.

A significant characteristic of UNIVAC is that it can read, write and compute simultaneously.

The UNIVAC is self-checking and the Central Computer contains two types of error detecting devices, companion checkers and odd-even checkers. The arithmetic circuits and most of the control circuits are duplicated, and the information in duplicate units is continuously compared. If a discrepancy occurs, the error circuits stop the computer and light a neon to indicate the unit in which the error occurred. Information is coded for the UNIVAC in such a way that the pulse pattern for each character must always contain an odd number of pulses. There are numerous odd-even checkers throughout the Central Computer. If a pulse pattern is detected which does not contain an odd number of pulses, the error circuits stop the computer and light a neon to indicate where the error was detected.

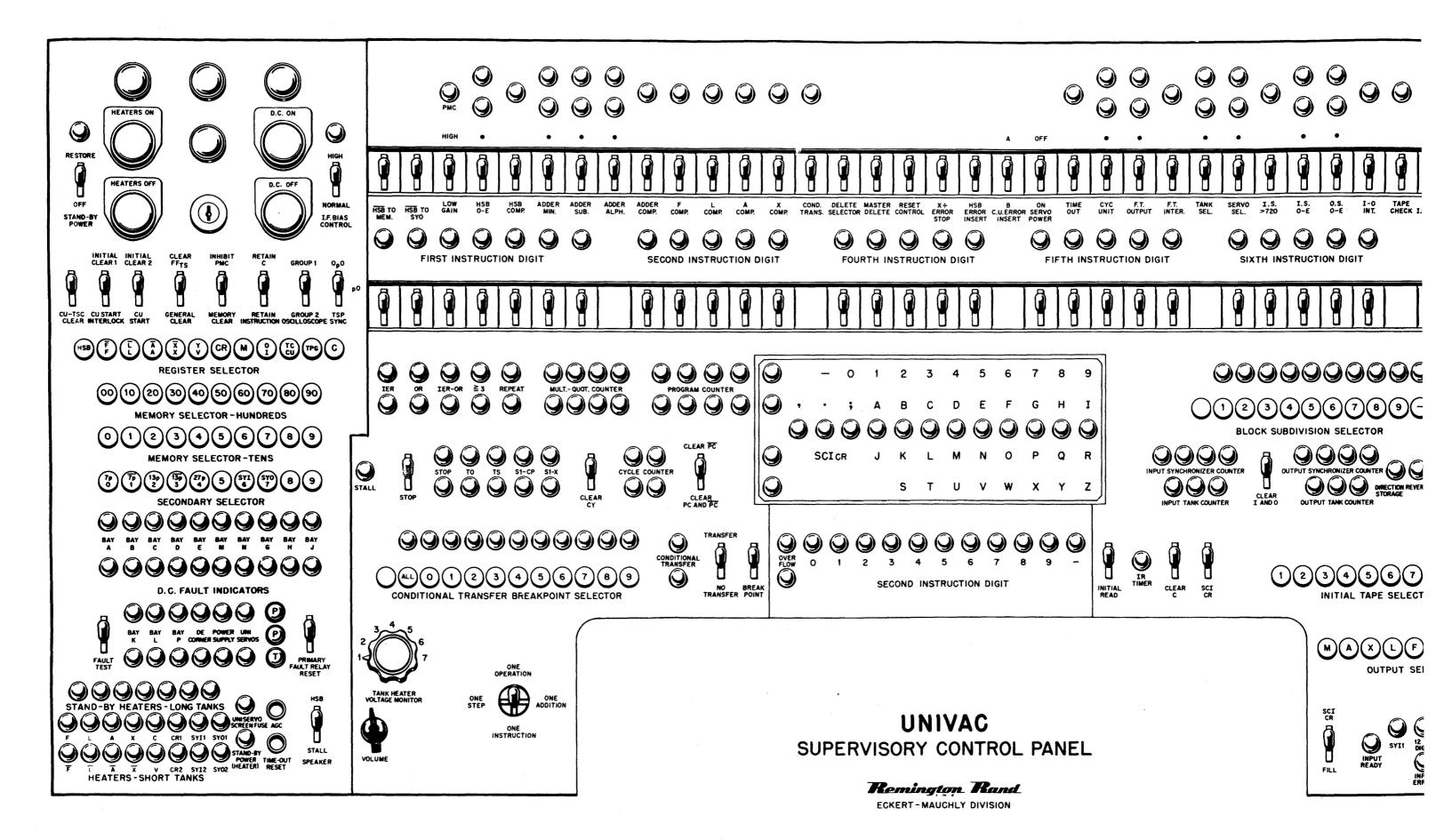

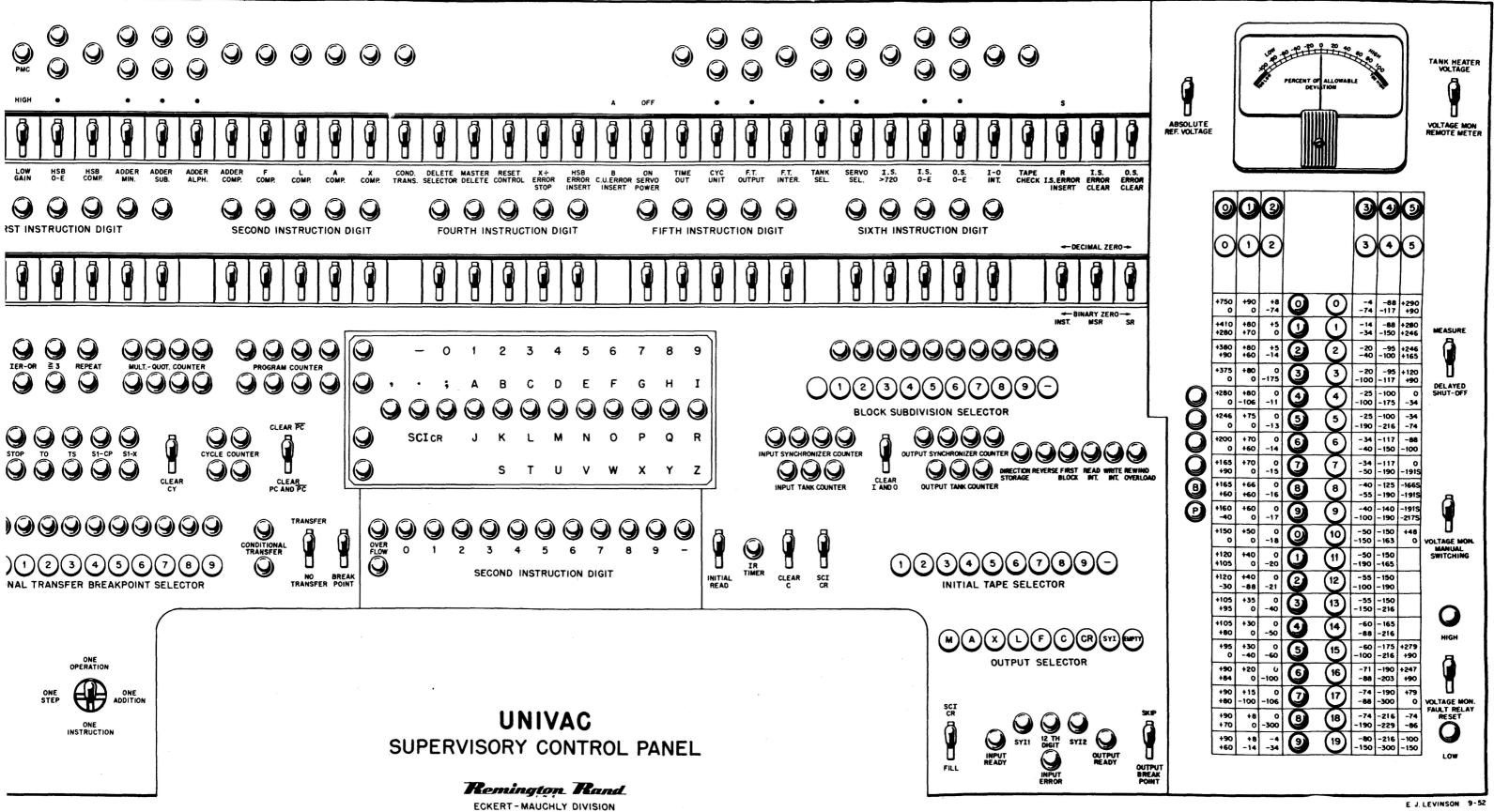

The Supervisory Control is an auxiliary device associated with the Central Computer. It contains the switches and signal lights for operating and servicing the computer. The error neons are located on the Supervisory Control panel. A printing unit and a keyboard similar to that of the UNITYPER are provided in the Supervisory Control. The operator maintains direct communication with the UNIVAC through the Supervisory Control. The operator can examine the contents of any part of the memory and every arithmetic register on an oscilloscope at the Supervisory Control. He can type in entries or corrections to the data in the computer, check intermediate results on the Supervisory Control Printer, and he can search for the origin of detected errors. The UNIVAC is designed to operate automatically. The Supervisory Control provides the operator with an intimate contact with the computer so that he can follow in detail the operations performed in the computer and can interfere with the sequence of events if he deems this desirable.

## SEC. 3. SOME APPLICATIONS OF THE UNIVAC SYSTEM

The UNIVAC System has proven its capabilities in the course of more than three UNIVAC-years of normal operation. It has solved numerous problems in each of four basic categories. These categories classify problem-solving according to the quantity of data processed and the amount of processing required for each unit of data.

<u>Category I</u> includes problems processing little inputoutput data and requiring little computation. Such problems, rarely repeated, demand more attention from the programmer than from the Central Computer and UNISERVOS. Exemplifying this type of problem is the calculation of the radiation pattern from a shaped antenna. This involved the evaluation of a definite integral by which the relative power radiated at each of a group of angles was computed from a system consisting of a feed horn working into a reflector "disk".

Problems involving little data but a large amount of processing fall into <u>Category II</u>. Here the heavy load is placed on the Central Computer, and little on the UNISERVOS. A Fourier summation was performed to produce tables for use in connection with an examination of the crystal structure of Banfield's and Kenyon's free radicals.

The third category puts heavy pressure on the operation of the UNISERVOS, but requires little effort on the part of the Central Computer. The selection of policies from a master file of an insurance company, for various types of processing, was so programmed that about 70,000 items could be examined each hour. From the master file arranged in order of district-policy number, those requiring premium notices were entered on one tape, those requiring either dividend or commission-processing on another, while a third tape received entries requiring special notifications. Control totals were maintained for checking purposes.

<u>Category IV</u> includes those problems which, requiring large quantities of input and output data, also require a large amount of processing. In general, such problems would not be attempted without the aid of a large computer. Outstanding in this class are the operations of matrix algebra. Programs have been prepared and applied for the multiplication, for the inversion, and for editing the results of these operations, for matrices of orders up to 300 by 300. The matrices are partitioned into submatrices of order ten by ten or less. One set of programs (low-level) performs the multiplication and inversion of the submatrices; another set (high-level) treats the submatrices as elements of the large matrix by directing the application of the low-level routines. The elements are treated in floating-decimal form. The elimination method with successive iterations to improve the error matrix gives an inversion time of 50 hours for a 200 by 200 matrix (See references XVIII and XIX in the bibliography).

The examples cited represent problems from engineering design, scientific research, commerce, and mathematics, and testify to the flexibility and universality of the UNIVAC System.

## SEC. 4. RESPONSIBILITIES OF THE PROGRAMMER

The types of problems that a programmer will be called upon to solve using a high-speed computer are multitudinous. Nevertheless, the task of the programmer can be conveniently broken down into four major parts--varying slightly from The first part includes the problemproblem to problem. analysis. The second part involves constructing a detailed logical outline of the solution of the problem and its translation into explicit instructions to the computer. The third part involves submitting the solution to the computer and obtaining the results. The fourth part is administrative including preparation of the report. These phases may occur in any chronological order, and one or more of these parts may be involved simultaneously in the handling of a problem; e.g., problem-analysis may very well continue from the start through the time that final results are obtained by the computer.

A more complete discussion of these four phases, which are the concern of a programmer, is included below as part of the introduction although much of the detail may be lost to a beginner. It is recommended, therefore, that at the conclusion of the first reading of the manual this section be studied again.

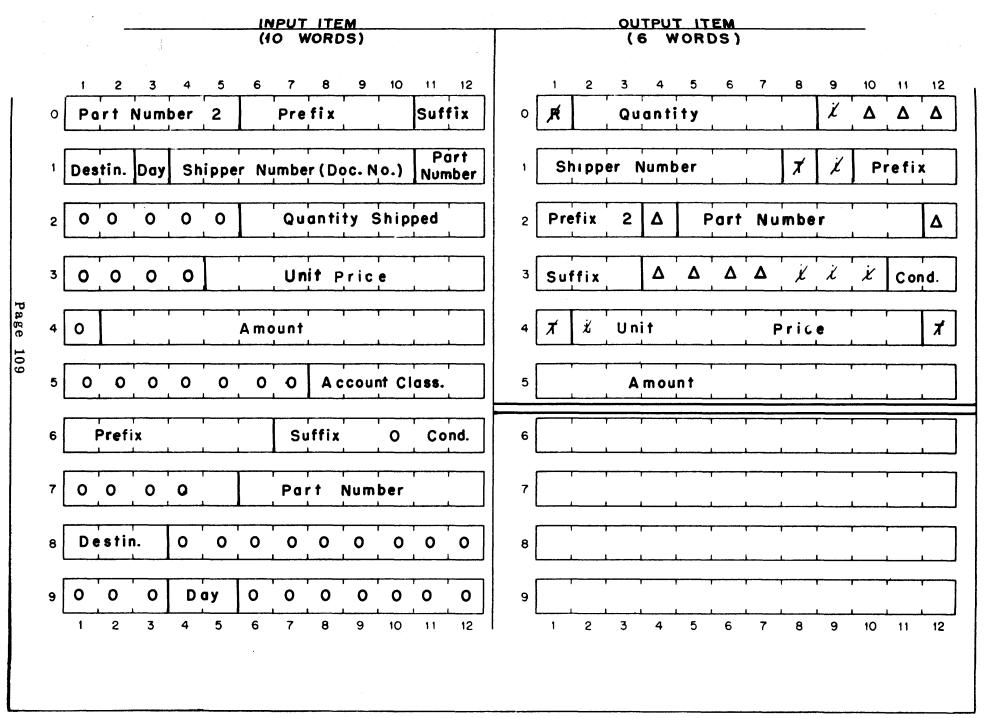

#### Problem-Analysis

Problem-analysis, first and foremost, requires that the problem be clearly defined. The programmer must be adamant in requiring a complete description of the problem, of the input data, of the form and volume of the desired output data, as well as of the computational or processing steps to be performed. In many cases a model, illustrating the problem, with sample input and output can be helpful. The problem analysis will include the study necessary to determine whether the current method of solution is to be accepted intact, or a new procedure better adapted to the computer is to be developed. Thus, the programmer determines what operations must be performed, and in what order they must be carried out.

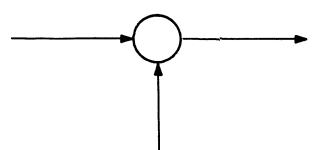

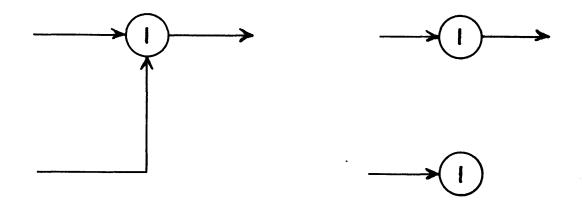

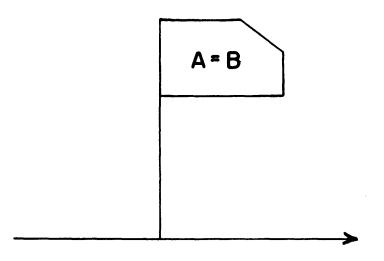

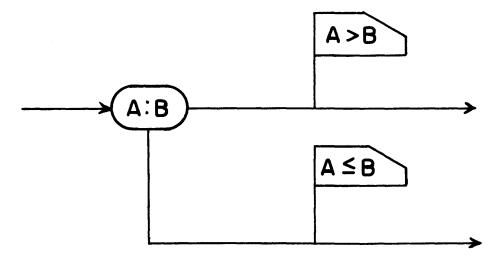

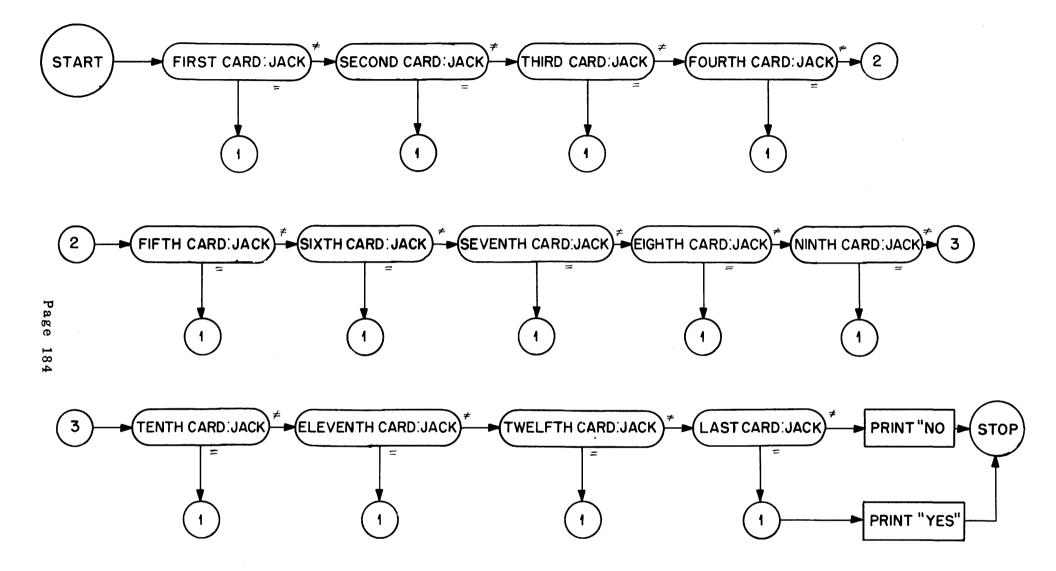

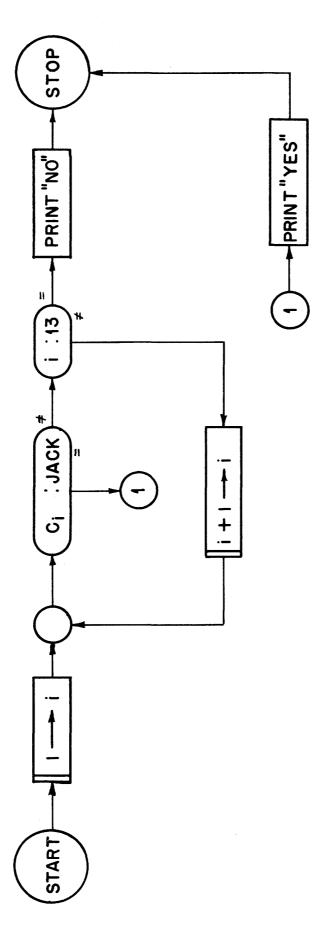

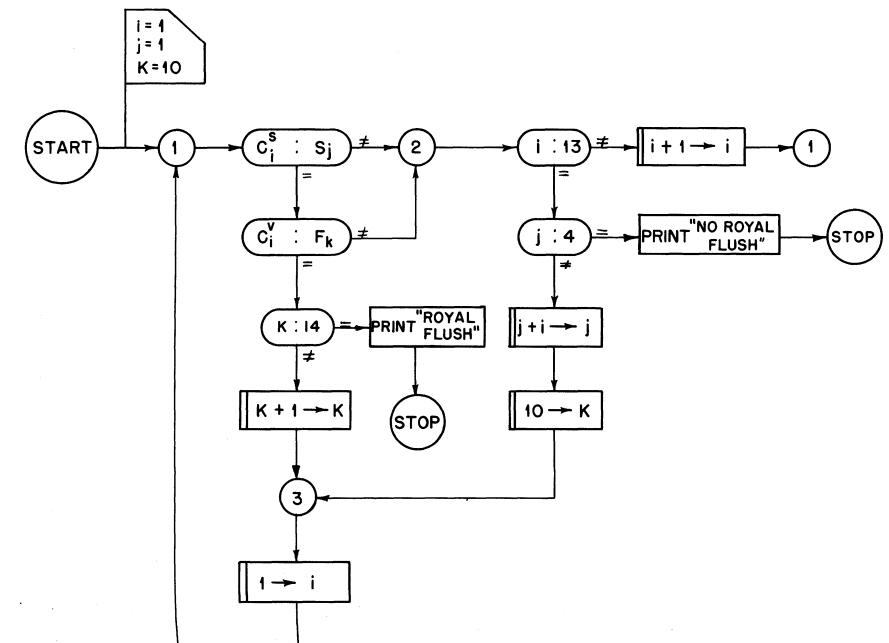

### Flow Charts and Coding

Proper analysis will enable the programmer to construct flow charts in sufficient detail to indicate the essential operations, logical as well as arithmetic, to be performed by the computer to achieve the solution to the problem. The flow-charts must contain enough detail to indicate clearly logical omissions, unnecessary operations, or errors in the contemplated "solution". The programmer must carefully review his flow-charts, for, if the flow-charts are correct, the problem might well be considered "solved".

However, this solution of the problem. in the form of flow-charts, is still meaningless to the computer. The operations indicated in the flow-charts must be translated into explicit instructions in the computer code.

After the coding is completed, it must be checked preferably by someone other than the original coder. The checking process cannot be overemphasized. It is imperative that the checker be thorough; not only must the coding itself be checked for errors, but the flow-charts must be examined for logical errors. Careful checking will save hours of grief in trying to run the problem on the computer. If the problem is mathematical in nature, a wise checker will run a numerical example on a desk calculator, following step-by-step each instruction in the coding. After the coding has been completed, the programmer must take a time-estimate for the problem - how long will it take to run on the computer?

#### Running the Problem on the Computer

After the coding has been completed and checked, it remains necessary to translate the written instructions from paper to the magnetic input tape of the computer. The instructions are transferred on the UNITYPER to tape and transcribed by a UNIPRINTER for proof-reading. It is essential that the programmer be satisfied beyond doubt that the correct information has been entered on the tape. If a problem involves a large amount of input data, it is wise to make arrangements to start the preparation of the input data well in advance of the expected date on which the problem is to be run. All reels of tape must be properly labeled, identifying the contents of the tapes. Space must be obtained for the filing of future tapes. Well in advance, the programmer should determine the number of tapes required for each problem-run.

Before the problem is run on the computer, the programmer must compile a set of operating instructions. The responsibility of operating the computer is great. The operator runs problems not for a single programmer, but for many programmers and he cannot know intuitively the characteristics of each problem. The operating instructions should indicate explicitly and clearly all the information that the operator requires to run the problem. What tapes are mounted on which UNISERVOS and when? What special settings are initially required on the Supervisory Control? What "typeins" are necessary and when? All of these questions and more must be answered in the operating instructions.

It is important for the programmer to realize from the beginning that it is the operator who actually runs the problem on the computer, performing all the physical operations at the Supervisory Control panel. The operator is a highly skilled and experienced man who is expert in the handling of the computer during a problem-run. The wise programmer will depend upon this knowledge and skill to run the problem efficiently with a minimum waste of valuable computer-time.

The programmer's chief role during a problem-run, especially during the initial run, is that of an observer, who satisfies himself that the problem is progressing properly. In the event that aprogramming error should arise, he should have some idea of where to begin looking for the error, and unless the error is almost immediately ascertained, the programmer may waste valuable computer time. Throughout a problem-run, a log of the operation is kept ... a record of past errors aids in avoiding the same pitfalls in the future.

After the computer run has been completed, and the results have been obtained on tape, the output tape must be filed for future references, the results must be printed, a complete report must be written. It is desirable to have the report of the problem, include coding, flow-charts, operating instructions, running times, discussions of new coding techniques, suggestions for improvement of the routine, and ideas for research. When <u>all</u> of this has been accomplished, the programmer may feel reasonably certain that his mission has been accomplished.

## Chapter 2

# Representation of Information

| Section | Торіс                                    | Page |

|---------|------------------------------------------|------|

| 1       | Preliminary Discussion                   | 15   |

| 2       | Decimal and Binary Systems of Notation   | 16   |

| 3       | The Binary Excess-Three System           | 17   |

| 4       | Practice Exercises                       | 18   |

| 5       | Excess-Three Complements                 | 19   |

| 6       | Practice Exercises                       | 20   |

| 7       | Excess-Three Additions                   | 20   |

| 8       | Practice Exercises                       | 22   |

| 9       | Excess-Three Subtractions                | 22   |

| 10      | Practice Exercises                       | 22   |

| 11      | Advantages of Binary Excess-Three System | 23   |

| 12      | Seven-Pulse Code                         | 23   |

| 13      | Internal Memory                          | 24   |

| 14      | A Computer "Word"                        | 24   |

| 15      | Digital Positions                        | 2 5  |

| 16      | Practice Exercises                       | 25   |

| 17      | Chart of UNIVAC Pulse Code               | 27   |

•

## SEC. I. PRELIMINARY DISCUSSION

In order for UNIVAC to perform the operations necessary to the solution of a problem, the computer must receive proper information. This information consists of certain defined arrangements of electronic pulses representing numeric, alphabetic and other typewriter symbols.

When a key of the UNITYPER is depressed, seven electric channels are activated and the resulting impulses create magnetic spots across the tape in accordance with the particular character involved.

It is the purpose of this chapter to present the relationships between the pulse patterns which UNIVAC accepts and the typewriter characters in which information is represented. To represent the variety of characters needed, UNI-VAC uses the binary system of notation which is a primary characteristic fundamental to most digital computers. For introductory purposes it is sufficient to state that the absence of an electrical pulse is represented by zero and the presence of a pulse is represented by one.

The relationship between typewriter characters and pulse combinations is shown in the table on the last page of this chapter. Reference to this table will show, for example, that

> 0 is represented 1 00 0011 5 is represented 0 00 1000 M is represented 1 10 0111

The first pulse position contains the check pulse and is not shown in the table. A discussion of this pulse position may be found in Section 12 of this Chapter. The next two pulse positions are known as the "zone indicators" and it will be noticed that both are zero for numeric characters.

## SEC. 2. DECIMAL AND BINARY SYSTEMS OF NOTATION

For a better understanding of the defined pulse combinations for numeric quantities employed by the UNIVAC system, it is advisable to discuss, more fully, the binary system of notation and its relation to the decimal system of notation. In the discussion to follow, numeric characters will be represented with only four pulse positions; the check pulse and "zone indicators" will be omitted. It must be remembered, however, that in the UNIVAC system all characters require seven pulse positions for representation.

In the <u>Decimal Notation</u>, the quantity three hundred fifty-nine is written in the decimal system, 359; i.e.,

$(3x10^2) + (5x10^1) + (9x10^0) = 300 + 50 + 9 = 359$  (1)

where

$$10^2 = 100$$

,  $10^1 = 10$ ,  $10^0 = 1$

The left hand side of the equality (1) shows the basic composition of the decimal, or "base ten" system. Each digit of (1) counting from right to left, is multiplied by successively higher powers of ten.

The binary system of notation uses two symbols (or digits) "O" and "1" as compared with the ten digits (O through 9) used in the decimal system. For example, the decimal quantity nine, expressed in the binary system, appears as 1001. This is equivalent to stating that

$$(1x2^3) + (0x2^2) + (0x2^1) + (1x2^0) = 8+0+0+1 = 9$$

(2)

where

$2^{3} = 8$ ,  $2^{2} = 4$ ,  $2^{1} = 2$ ,  $2^{0} = 1$ .

The left-hand side of the equality shows the basic composition of the binary or "base two" system. Each digit of (2), counting from right to left, is multiplied by successively higher powers of two. Hence, the decimal quantities and their binary equivalents are as shown in the following table.

Page 16

| Decimal | Binary |

|---------|--------|

| 0       | 0000   |

| 1       | 0001   |

| 2       | 0010   |

| 3       | 0011   |

| 4       | 0100   |

| 5       | 0101   |

| 6       | 0110   |

| 7       | 0111   |

| 8       | 1000   |

| 9       | 1001   |

| 10      | 1010   |

| 11      | 1011   |

| 12      | 1100   |

| 13      | 1101   |

| 14      | 1110   |

| 15      | 1111   |

## Table of Decimal and Binary Equivalents

## SEC. 3. THE BINARY EXCESS-THREE SYSTEM

UNIVAC uses a modified binary code, called the excessthree system. Each decimal digit is represented, in binary, by its original value plus three. Reasons, justifying the use of the "excess-three" system rather than the pure binary system, are given below in Section 11. In later discussions the symbols "O" and "1" used in the excess-three system will be referred to as binary zero and binary 1.

Table of Decimal and Excess-Three Equivalents

| <u>Decimal</u> | Decimal<br>Excess-<br><u>Three</u> | Binary<br>Excess-<br><u>Three</u> |

|----------------|------------------------------------|-----------------------------------|

| 0              | 3                                  | 0011                              |

| 1              | 4                                  | 0100                              |

| 2              | 5                                  | 0101                              |

| 3              | 6                                  | 0110                              |

| 4              | 7                                  | 0111                              |

| 5              | 8                                  | 1000                              |

| 6              | 9                                  | 1001                              |

| 7              | 10                                 | 1010                              |

| 8              | 11                                 | 1011                              |

| 9              | 12                                 | 1100                              |

|                | _                                  |                                   |

Chapter 2

```

Thus, 724 = 1010 \quad 0101 \quad 0111

```

where 7 = 10102 = 01014 = 0111

It should be clear that the UNIVAC system considers each digit of a quantity in binary excess-three notation which is somewhat different from the usual binary notation. For example the number 25 in the usual binary notations equals

$16+8+1 = 1(2^4)+1(2^3)+0(2^2)+0(2^1)+1(2^0) = 11001$

But in digital binary (excess-three) notation

5

25 = 0101 1000

2

SEC. 4. PRACTICE EXERCISES ON EXCESS-THREE REPRESENTATION

Represent the following quantities in binary excessthree notation. (Ignore zone indicators and check pulse).

- 1. 23

- 2. 407

- 3. 5891

What would be the 6-pulse code representation of the following quantities. (Ignore the check pulse).

- 4. B 100

- 5. T2 325

- 6. A- 000

## Chapter 2

SEC. 5. EXCESS-THREE COMPLEMENTS

If two positive quantities when added together, produce a power of ten, one is said to be the ten's complement of the other. For example, the ten's complement of 724 is 276, since 724 + 276 = 1000; the ten's complement of 51 is 49, for 51 + 49 = 100. Subtraction is performed by adding the complement of the subtrahend to the minuend. Carry resulting from the sum of the most significant digits is ignored. For example,

892 - 724 = 168,

using complements, 892 + 276 = 168.

In the excess-three system, complements on <u>nine</u> are obtained by substituting zeros for ones and ones for zeros. Hence, complements on <u>ten</u>. would be obtained by increasing by one the least significant decimal digit of the nine's complement

thus

4 = 0111

5 = 1000 = nine's complement of four

6 = 1001 = ten's complement of four

also

724 = 1010 0101 0111 275 = 0101 1010 1000 = nine's complement of 724 276 = 0101 1010 1001 = ten's complement of 724

| <u>Decimal</u> | Excess-Three | Excess-Three<br>Nine's Complement |

|----------------|--------------|-----------------------------------|

| 0              | 0011         | 1100                              |

| 1              | 0100         | 1011                              |

| 2              | 0101         | 1010                              |

| 3              | 0110         | 1001                              |

| 4              | 0111         | 1000                              |

| 5              | 1000         | 0111                              |

| 6              | 1001         | 0110                              |

| 7              | 1010         | 0101                              |

| 8              | 1011         | 0100                              |

| 9              | 1100         | 0011                              |

It will be understood that when complements are referred to in succeeding exercises and discussions, <u>tens</u>' complements are implied.

## SEC. 6. PRACTICE EXERCISES

Represent the complements of the following in excessthree notation (ignore zone indicators and check pulse)

- 1. 42

- 2. 436

- 3. 510

- 4. 7777

## SEC. 7. EXCESS-THREE ADDITIONS

When two decimal digits are added which do not produce a ten's carry, the corresponding binary addition of their excess-three representations will exceed the correct sum by an excess-three; i.e., the sum is too great by an excessthree correction:

| Decimal  | <u>Excess-Three</u>   | Decimal | Excess-Three           |

|----------|-----------------------|---------|------------------------|

| 1        | 0100                  | 4       | 0111                   |

| <u>3</u> | 0110                  | 5       | 1000                   |

| 4        | $\overline{1010} = 7$ | 9       | $\overline{1111} = 12$ |

Page 20

Hence, if no carry occurs when two digits are added, an excess-three must be subtracted (complement of excess-three, 1101, added) from that digit to produce the correct sum. In performing excess-three corrections, no carry is executed from decimal digit to decimal digit.

When two decimal digits are added to produce a ten's carry, the corresponding binary addition of their excessthree representations will produce a carry from the fourth binary digit position. Thus, the excess-three correction is missing from the sum digit; i.e., the sum is deficient by an excess-three correction:

| Decimal                | Excess-Three                                 | Decimal            | Excess-Three            |

|------------------------|----------------------------------------------|--------------------|-------------------------|

| 8<br><u>7</u><br>Sum 5 | $\frac{1011}{1010} \\ \frac{1010}{0101} = 2$ | 9<br><u>9</u><br>8 | $\frac{1100}{1000} = 5$ |

| Carry                  |                                              |                    |                         |

| 1                      | 1                                            | 1                  | 1                       |

Hence, if a carry occurs when two digits are added, an excess-three must be added to that digit to produce the correct sum.

| Example 1. | Add  | 592 and | 257. |                              |

|------------|------|---------|------|------------------------------|

| 592 =      | 1000 | 1100    | 0101 |                              |

| 257 =      | 0101 | 1000    | 1010 |                              |

|            | 1101 | 0100    | 1111 | ·                            |

|            | 1    |         |      | carry                        |

|            | 1110 | 0100    | 1111 |                              |

|            |      | 0011    |      | correction if carry, + XS3   |

|            | 1101 |         | 1101 | correction if no carry, -XS3 |

| 849 =      | 1011 | 0111    | 1100 |                              |

SEC. 8. PRACTICE EXERCISES

Perform the following additions by means of the binary excess-three method.

- 1. Add 3 and 4.

- 2. Add 9 and 5.

- 3. Add 25 and 40.

- 4. Add 18 and 46.

- 5. Add 478 and 903.

SEC. 9. EXCESS-THREE SUBTRACTION

Excess-three differences are obtained by adding the complement of the quantity, smaller in absolute magnitude, to the larger, and appending the sign of the larger.

Example 1: 72 - 34 = 38, using complements 72 + 66 = 38. In the excess-three system,

|            |    | 72        | = | 1010 | 0101              |            |    |                |

|------------|----|-----------|---|------|-------------------|------------|----|----------------|

|            |    | 34        | = | 0110 | 0111              |            |    |                |

| complement | οf | 34        | = | 1001 | 1001.             |            |    |                |

| Hence,     |    | 72        | = | 1010 | 0101              |            |    |                |

| complement | οf | <u>34</u> | = |      | <u>1001</u>       |            |    |                |

|            |    |           |   | 0011 | 1110              |            |    |                |

|            |    | 1         |   |      |                   | carry      |    |                |

|            |    |           |   | 0011 |                   | correction | if | carry, + XS3   |

|            |    |           |   |      | <u>1101</u>       | correction | if | no carry, -XS3 |

|            |    | 38        | = | 0110 | $\overline{1011}$ |            |    |                |

SEC. IO. PRACTICE EXERCISES

Perform the following subtractions by means of the excess-three method. Add the complement of the smaller quantity to the larger quantity and append the sign of the larger.

- 1. 8 2

- 2. 82 55

- 3. 100 17

- 4. 325 109

- 5. 109 325

SEC. II. ADVANTAGES OF BINARY EXCESS-THREE SYSTEM

Two of the advantages in using the binary excessthree system are:

(a) It is electronically easy to represent complements on ten in this system.

(b) A "carry" in the decimal system will produce a "carry" in the binary excess-three system, (e.g.) the addition of 6 and 5 in the three systems are:

| <u>Decimal</u> | Binary | Binary<br>Excess-<br><u>Th ree</u> |

|----------------|--------|------------------------------------|

| 6              | 0110   | 1001                               |

| 5              | 0101   | 1000                               |

| $\overline{1}$ | 1011   | 0001                               |

carry 1 no carry carry 1

SEC. 12. SEVEN-PULSE CODE

The seventh pulse position which is added will contain a "check-pulse" designed to detect the gain or loss of a binary pulse. The check pulse is present, or absent, according as it is, or is not, necessary to make the number of pulses representing any character odd. For example,  $A = 01\ 0100$  requires a check pulse in order that an odd number of pulses be present,  $A = 1\ 01\ 0100$ ; so also  $6 = 00\ 1001$  becomes  $6 = 1\ 00\ 1001$ . On the other hand, no check pulse is required by  $C = 01\ 0110$  which becomes C = $0\ 01\ 0110$ . Frequent checks are made throughout the computer circuits to insure that each character is represented by an odd number of pulses.

#### SEC. 13. INTERNAL MEMORY

The internal memory of the UNIVAC consists of acoustic delay lines. It contains 100 channels, each storing ten words. The "memory locations" of the 1000 words are numbered from 000 to 999. Every five seconds the entire content of the memory is automatically checked to insure the continued correctness of the stored information.

Transfer of data into a memory location automatically erases any information previously stored in that location. However, reading from a memory location does not destroy its contents. The symbol, (), is used to mean "the contents of"; i.e., (m) = the contents of memory location m in the computer, m being any number from 000 to 999.

#### SEC. 14. A COMPUTER "WORD"

Each memory location holds one "word" of information consisting of twelve characters. A "word" of information can be coded to take one of two forms:

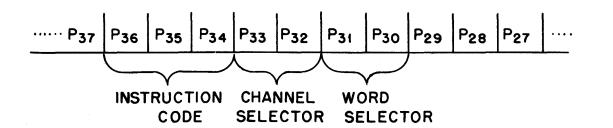

(a) It may consist of twelve characters, representing a numeric quantity or other data to be processed. When it is a numeric quantity, the twelve characters in the word are the algebraic sign, followed by eleven decimal digits. A "zero" in the sign position represents a plus sign. The computer in performing multiplication and division, considers the decimal point to lie immediately to the right of the sign position. Thus, all quantities X, are treated as falling in the range -1 < X < +1. It will be seen later how quantities outside this range are handled. (b) Or it may take the form of two "instructions" to the computer (e.g.)

## B00120 C00185

Each instruction consists of six computer digits. The first two characters in each instruction designate the operation to be performed (and will be defined in succeeding chapters) and the fourth, fifth and sixth digits in each instruction designate a memory location. The third digit (underlined and usually not written) is not decoded.

The computer performs the two instructions serially; the right instruction is executed after the left instruction has been accomplished.

## SEC. 15. DIGITAL POSITIONS

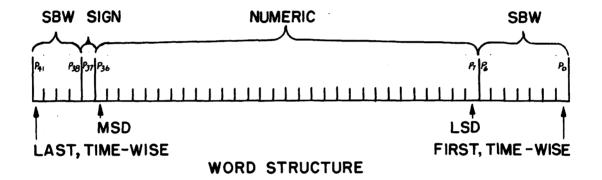

In later discussions, reference will be made to digital positions and, hence, some comment on this terminology is in order. Consider the twelve digital positions of a computer word,

The location labeled  $\underline{1}$  is the first digit position and contains the sign of a numeric quantity. The location labeled  $\underline{2}$  is referred to as the most significant digit (MSD) position and location  $\underline{12}$ , the least significant digit (LSD) position. When discussing non-numeric words, it is usually better to refer to the digital positions 1 to 12.

## SEC. 16. PRACTICE EXERCISES

Using the seven-pulse code, in exercises 1 to 4, represent the quantities:

- 1. A 425

- 2. R 310 U 100

- 3. *ž*

- 4. A decimal zero.

Chapter 2

Represent the following quantities in the seven-pulse code, perform the operations indicated and represent the result in seven pulses.

- 5. 5076 + 2438

- 6. 3247 1066.

.

SECTION 17 - UNIVAC PULSE CODE

| ZONE |      | X\$3 |              |      |      |      |      |      |      |       |      |      |      |      |      |      |

|------|------|------|--------------|------|------|------|------|------|------|-------|------|------|------|------|------|------|

| ZONE | 0000 | 0001 | 0010         | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 100 1 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

| 00   | ž    | Δ    | -            | 0    | 1    | 2    | 3    | 4    | 5    | 6     | 7    | 8    | 9    |      |      |      |

| 0 1  | Ŕ    | 3    | •            | ;    | A    | В    | с    | D    | E    | F     | G    | н    | I    |      |      |      |

| 10   | 7    |      | $\mathbf{X}$ | 1    | J    | к    | L    | м    | N    | 0     | Р    | Q    | R    | ¥    |      | þ    |

| 1 1  | P    | ø    |              |      | +    | S    | т    | U    | v    | w     | x    | Y    | z    | ø    |      |      |

- i = IGNORE

- Δ = SPACE

- R = CARRIAGE RETURN

- **7' = TAB**

- K = SHIFT LOCK

- Ø = UNSHIFT

- Ø = ONE SHIFT (SINGLE SHIFT)

- **P** = PRINTER STOP

- **B** = **PRINTER BREAKPOINT STOP**

- ☑ = NOT AVAILABLE (USED INTERNALLY)

- BLANK SQUARES NOT USED.

NOTE - IN GENERAL, UNITYPER HAS A STANDARD KEYBOARD, BUT OTHER TYPEWRITER SYMBOLS CAN BE, AND HAVE BEEN PROVIDED.

# Chapter 3

# Registers

| Section | Торіс                                                | Page                 |

|---------|------------------------------------------------------|----------------------|

| 1       | Preliminary Discussion                               | 28                   |

| 2       | Registers CC and CR                                  | 29                   |

| 3       | One-Word Registers A,X,L,F                           | 29                   |

| 4       | Multi-Word Registers V,Y,I,O                         | 30                   |

| 5       | One-Word Transfers Using                             |                      |

|         | Register A<br>Register X<br>Register F               | 31<br>31<br>32       |

| 6       | Multi-Word Transfers Using                           |                      |

|         | Register V<br>Register Y<br>Register I<br>Register O | 33<br>35<br>36<br>36 |

| 7       | Practice Exercises                                   | 37                   |

## SEC. I. PRELIMINARY DISCUSSION

In Chapter 2 it was stated that the internal memory of UNIVAC consists of memory locations capable of storing 1000 words. UNIVAC also employs certain additional "storage facilities" called registers, the functions of which are quite different from those of memory locations.

When instructions and other data are transferred to the computer from magnetic tape, they are placed into memory locations, and retained there until called upon to take part in the procedures. As these data are required for computation and other operations, they are processed through the registers. These registers are used, then, to

- (a) Transfer data between memory locations.

- (b) Perform arithmetic and control operations.

It is the purpose of this chapter to discuss these registers and define the part they play in the processing of instructions and other data. In Chapter 9, the role of registers in the total logical pattern will be presented. It should be noted, first, that a register is said to be "erased" when it contains binary zeros. A register is said to be "cleared" when decimal zeros (in the excess-three code) replace its previous contents.

Several registers are required for temporary storage of data being processed by the computer. Two of these are oneword registers used for sequencing operations (CC,CR); four are one-word registers used for arithmetic and logical operations (rA, rX, rL, rF); four are multi-word registers used to transfer data (rV, rY, rI, rO).

It has been stated that transfer of data into a memory location automatically erases any information previously stored in that location. Similarly, a transfer of data into a register (except rI) erases information previously stored. However, unlike memory locations, <u>reading from</u> a register may, depending on the instructions, also clear the register of its previous contents. The action in rI, under such conditions, will be discussed in Chapter 8. Throughout this manual, the symbol "m" represents a memory location number.

## SEC. 2. REGISTERS CC AND CR

These two registers are concerned with the sequencing of control operations.

The <u>control counter</u> (CC) stores the number of the memory location containing the next pair of instructions to be executed.

The <u>control register</u> (CR) stores the current pair of instructions.

Further discussion of these two registers will be delayed until Chapter 8.

SEC. 3. ONE-WORD REGISTERS

The four registers, rA, rX, rL, and rF, are duplicated within the computer. The contents of the duplicated registers are continuously compared by checking circuits which immediately detect any discrepancy between the duplicated quantities.

Register A is used for:

- (a) one-word transfers

- (b) storing the addend (minuend) in addition (subtraction)

- (c) retaining a partial or complete algebraic sum

- (d) storing the more significant half of a twenty-two digit product or a rounded eleven digit product after multiplication

- (e) storing the dividend at the start of division

- (f) storing the rounded quotient after division

- (g) retaining a quantity to be shifted right or left, and performing the shift

- (h) assembling extracted quantities

Registers

(i) storing one component of a comparison

Register X is used for:

- (a) one-word transfers

- (b) storing the augend (subtrahend) in addition (subtraction)

- (c) storing the multiplier during multiplication

- (d) storing the less significant half of a twentytwo digit product after multiplication

- (e) storing the unrounded quotient after division

Register L is used for:

- (a) storing the multiplicand during multiplication

- (b) storing the divisor during division

- (c) storing one component of a comparison

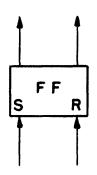

Register F is used for:

- (a) one-word transfers

- (b) storing the extractor

- (c) storing three times the absolute magnitude of the multiplicand during multiplication.

#### SEC. 4. MULTI-WORD REGISTERS

Register V is used for two-word transfers

Register Y is used for ten-word transfers

- <u>Register I</u> is used to assemble "one block", 60 words, read from tape for transfer into the memory.

- <u>Register O</u> is used to store one block from the memory until written on tape.

## SEC. 5. ONE-WORD TRANSFERS

Register A

| Instructio | <u>in s</u>                                   |

|------------|-----------------------------------------------|

| Bm         | Erase rA and rX; transfer (m) to rA and rX.   |

| Cm         | Transfer (rA) to m; clear rA to decimal zeros |

| Hm         | Transfer (rA) to m; do not alter rA           |

| Km         | Transfer (rA) to rL clear rA; ignore m.       |

A complete one-word transfer using rA involves two instructions; (a) transferring a quantity from the memory to rA, and (b) transferring the quantity from rA to the memory.

Example 1: (050) = a. Transfer "a" to 051 and 052.

| Mem.<br>Loc. | Instruction    | <u>Remarks</u>                        |

|--------------|----------------|---------------------------------------|

| 020          | B 050<br>H 051 | a> rA and $rX(rA) = a> 051; (rA) = a$ |

| 021          | C 052          | (rA) = a> 052; 0> rA                  |

Register X

| Instructio | ons                                         |

|------------|---------------------------------------------|

| Bm         | Erase rA and rX; transfer (m) to rA and rX. |

| Lm         | Erase rL and rX; transfer (m) to rL and rX. |

| Jm         | Transfer (rX) to m; do not erase rX.        |

A complete one-word transfer using rX involves two instructions; (a) transferring a quantity from the memory to rX, and (b) transferring the quantity from rX to the memory.

Example 1: (050) = a. Transfer "a" to 051 and 052.

| Mem.<br>Loc.           | Instruction         | Remarks                                          |

|------------------------|---------------------|--------------------------------------------------|

| 0 20                   | B 050               | $a \rightarrow rA$ and $rX$                      |

| 021                    | J 052               | (rA) = a> 051; 0> rA<br>(rX) = a> 052; (rX) = a. |

| Example 2:<br>ing (rA) | (050) = a. Transfer | "a" to 051 without disturb-                      |

| Mem.<br>Loc.           | Instruction         | Remarks                                          |

| 020                    | L 050<br>J 051      | a> rL and rX<br>(rX) = a> 051; (rX) = a.         |

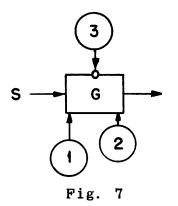

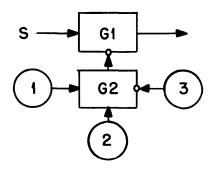

Register F

| Instructio | on s                                 |

|------------|--------------------------------------|

| Fm         | Erase rF; transfer (m) to rF.        |

| Gm         | Transfer (rF) to m; do not erase rF. |

A complete one-word transfer using rF involves two instructions; (a) transferring a quantity from the memory to rF, and (b) transferring the quantity from rF to the memory.

Example 1: (050) = a. Transfer "a" to 051, without disturbing (rA) or (rL). Mem. Instruction Remarks Loc. a --> rF0 20 F 050 G 051 (rF) = a --> 051; (rF) = a.Interchange: Two quantities may be interchanged by means of one-word transfers. Example 1: (050) = a. (051) = b. Interchange "a" and "b". Mem. Loc. Instruction Remarks 0 20 050 В  $a \rightarrow rA$  and rXL 051 b --> rL and rX021 (rA) = a --> 051; 0 --> rAС 051 J 050 (rX) = b --> 050; (rX) = b.SEC. 6. MULTI-WORD TRANSFERS

All multi-word transfers erase the registers or memory locations to which they are directed with the exception of rI.

Register V

| <u>Instru</u> | ctions                                                                                                                                                                  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vm            | Erase rV; transfer two consecutive words, start-<br>ing with m, to rV; m is usually a multiple of<br>two. For other cases see paragraphs to follow.                     |

| Wm            | Transfer (rV) to two consecutive memory locations,<br>starting with m; do not erase rV; m is usually a<br>multiple of two. For other cases see paragraphs<br>to follow. |

A complete two-word transfer using rV involves the two instructions: (a) transferring two successive words from the memory to rV, and (b) transferring the two quantities from rV to the memory.

Example 1: (050) = a, (051) = b. Transfer "a" and "b" to 096 and 097 respectively.

Mem.

Loc. Instruction Remarks

020 V 050 a, b --> rV W 096 a -->096; b -->097; (rV) = a, b.

If the m in both the Vm and Wm instructions is odd and the least significant digit is not equal to nine, the instructions behave as in the following example.

Example 2: (051) = a, (052) = b. Transfer "a" and "b" to 063 and 064 respectively.

Mem.

Loc. Instruction Remarks

020 V 051 a, b --> rVW 063 a--> 063; b --> 064; (rV) = a, b.

If the m in one instruction is odd (least significant digit not equal to nine), and the m of the other instruction is even, the two words are transferred in reversed order.

Example 3: (051) = a, (052) = b. Transfer "b" followed by "a" to 054 and 055 respectively.

Mem.

Loc. Instructions Remarks

020 V 051 a, b --> rV W 054 b --> 054; a --> 055; (rV) = a, b.

Example 4: (050) = a, (051) = b. Transfer "b" followed by "a" to 063 and 064 respectively.

Mem.

Loc. Instruction Remarks

| 0 20 | V | 050 |   |     | a, b $>$ rV                         |   |  |

|------|---|-----|---|-----|-------------------------------------|---|--|

|      |   |     | W | 063 | b $> 063$ ; a $> 064$ ; (rV) = a, b | b |  |

If the m in a Vm or Wm instruction has a nine as its least significant digit, the instruction will transfer from, or to, the last and first words in the ten-word memory channel.

Example 5: (050) = a, (059) = b. Transfer "a" followed by "b" to 100 and 101.

Mem.

| Loc. | Instruction | Remarks  |

|------|-------------|----------|

| 0 20 | V 059       | b, a> rV |

W 100 a --> 100; b --> 101; (rV) = b, a.

Register Y

InstructionsYmErase rY; transfer ten consecutive words start-<br/>ing with m, to rY; m should be an integral multi-<br/>ple of tenZmTransfer (rY) to ten consecutive memory locations<br/>starting with m; do not erase rY; m should be an<br/>integral multiple of ten

A complete ten-word transfer using rY involves two instructions; (a) transferring ten successive words from the memory to rY, and (b) transferring the ten quantities from rY to the memory.

Example 1:  $(050) = a_0$ ,  $(051) = a_1$ ,...,  $(059) = a_9$ . Transfer " $a_0$ ,...,  $a_9$ " to 100,..., 109 respectively

Mem.

Loc. Instruction Remarks

020 Y 050  $a_0, \ldots, a_9 \longrightarrow rY$ Z 100  $a_0, \ldots, a_9 \longrightarrow rY$  $(rY) = a_0, \ldots, a_9$ .

When executing a Ym or Zm instruction, the least significant digit of m is ignored by the computer. The transfers operate on the integral multiples of ten. Thus, Y999 is equivalent to Y990, and Z784 to Z780.

Register I

Register I does <u>not</u> erase upon read in, but only upon transferral of its contents to the memory. The tape instructions reading into rI will be discussed in Chapter 8.

Instructions30mTransfer sixty words stored in rI to sixty<br/>consecutive memory locations, starting with<br/>40m40mm; m should be an integral multiple of ten;<br/>erase rI.

Register O

Register 0 holds sixty words during a write instruction. Register 0 cannot be used independently of the tape instructions which will be discussed in Chapter 8. SEC. 7. PRACTICE EXERCISES

Problems on the transfer of data

Given

$(052) = x_{1}$   $(053) = x_{2}$   $(053) = x_{3}$   $(054) = x_{3}$   $(055) = x_{4}$   $(056) = x_{5}$   $(057) = x_{6}$   $(058) = x_{7}$   $(059) = x_{8}$   $(060) = x_{9}$   $(061) = x_{10}$

In each of the following problems write the instructions to perform the operations indicated; start with memory location 020. Choose any unused memory locations for working storage.

1. Transfer quantity  $x_1$  to 050 and 051 using

(a) rA (b) rX

(c) rF

2. Transfer quantity  $x_1$  to 050 and 053 and place  $x_2$  in 052.

- 3. Transfer  $x_1$  to 053,  $x_2$  to 054,  $x_3$  to 053 and clear rA.

- 4. Transfer  $x_1$  to 048 and 046,  $x_2$  to 049 and 045 using the V, W instructions.

- 5. Move the given 10 quantities up two memory locations i.e.,  $x_1 = -2050$ ,  $x_2 = -2051$ ,  $x_3 = -2052$ , ...  $x_{10} = -2059$

# Fundamental Arithmetic Operations

| SECTION | TOPIC                                                   | PAGE     |

|---------|---------------------------------------------------------|----------|

| 1       | Preliminary Discussion                                  | 39       |

| 2       | Addition                                                | 40       |

| 3       | Practice Exercises                                      | 42       |

| 4       | Subtraction                                             | 43       |

| 5       | Practice Exercises                                      | 44       |

| 6       | Multiplication                                          | 45       |

| 7       | Practice Exercises                                      | 47       |

| 8       | Division                                                | 48       |

| 9       | Practice Exercises                                      | 49       |

| 10      | Review Practice Exercises                               | 50       |

| 11      | Special Consideration in<br>Arithmetic Computation      | 50       |

|         | Addition and Subtraction<br>Multiplication and Division | 50<br>55 |

| 12      | Practice Exercises                                      | 56       |

## SEC. I. PRELIMINARY DISCUSSION

The purpose of this chapter is to explain UNIVAC instructions for addition, subtraction, multiplication, division and to consider certain special problems closely allied to these operations. Before delving into these details, it is advisable to review some concepts, previously discussed.

(a) The internal memory of UNIVAC consists of 100 channels, each storing ten words. The "memory locations" of the 1000 words are numbered from 000 through 999.

(b) A "word" may have the form of two instructions or may be information composed of twelve typewriter characters.

(c) The instructions in a "computer word" are executed serially, first the left instruction followed by the right instruction.

(d) The symbol (m) represents "the contents of memory location m."

(e) A transfer into a memory location erases any information previously stored in that location but reading from a memory location does not destroy its contents.

(f) There are four one-word registers - rA, rX, rL, rF; the multi-word registers are rV, rY, rI, rO.

(g) A complete transfer involves two instructions -transferring a quantity from a memory location to a register, and then, transferring the quantity from the register to a memory location.

In the performance of arithmetic processes, certain special conditions may arise and must be recognized. Two of these problems will be mentioned, briefly, and considered in more detail in later discussions. (a) The algebraic addition, subtraction or division of numeric quantities, considered as decimals by UNIVAC, may lead to results greater than plus one or less than minus one. This situation, called "overflow" must be handled by special techniques which will be described in Chapter 7.

(b) In the study of instructions for arithmetic manipulation, the question may arise as to computer responses to quantities that contain characters, other than numeric. A discussion of this problem will be found at the end of this chapter.

Finally, it will be noted that the instructions, previously defined, are restated in this chapter. A complete table of instructions may be found at the back of this manual and it is so placed for easy reference.

## SEC. 2. ADDITION

| Instructi | <u>ons</u>                                                                            |

|-----------|---------------------------------------------------------------------------------------|

| Am        | Transfer (m) to rX; add (rX) to rA); deliver<br>the sum to rA; do not erase rX.       |

| Bm        | Erase rA and rX; transfer (m) to rA and rX.                                           |

| Cm        | Transfer(rA) to m; clear rA.                                                          |

| Hm        | Transfer (rA) to m; do not clear rA.                                                  |

| Jm        | Transfer (rX) to m; do not erase rX.                                                  |

| Km        | Transfer (rA) to rL; clear rA; ignore m.                                              |

| Sm        | Transfer -(m) to rX; add (rX) to (rA); deliver the difference to rA; do not erase rX. |

| Xm        | Add (rX) to (rA); deliver the sum to rA; do not erase rX; ignore m.                   |

A complete addition involves three instructions; (a) transferring the addend to rA, (b) transferring the augend to rX, adding (rX) to (rA), and delivering the sum to rA, and (c) transferring the sum from rA to the memory. Example 1: (049) = x, (050) = y. Deliver the sum x+y = z to 051. Mem. Loc. Instruction Remarks 0 20 B 049  $x \rightarrow rA$  and rXA 050 y --> rX; x+y = z --> rA021 C 051 (rA) = z --> 051; 0 --> rA.(049) = x, (050) = y. Deliver the sum p = x+y+yExample 2: to 051. Mem. Loc. Instruction Remarks  $x \rightarrow rA$  and rX0.20 B 049 y --> rX; x+y = z --> rA; (rX)=yA 050 z+y = p --> rA021 Х 000 C 051 (rA) = p --> 051; 0 --> rA.Example 3: (049) = x, (050) = y, (051) = z. Deliver the sum x+y = p to 052, and the sum x+y+z = q to 053. Mem. Loc. Instruction Remarks 0 20  $x \rightarrow rA$  and rXB 049 y --> rX; x+y = p --> rA; (rX)=yA 050 021 052 (rA) = p --> 052; (rA) = pΗ z --> rX; p+z = q --> rA; (rX) = zA 051 (rA) = q --> 053; 0 --> rA.022 C 053

SEC. 3. PRACTICE EXERCISES ON ADDITION

In the problems to follow:

(049) = X, (050) = Y, (051) = Z

use any memory location for working storage. Write the instructions to:

1. Deliver 3x to 060.

2. Deliver the sum x+2y to 060.

3. Deliver the sum 2x+3y to 060.

4. Deliver the sum 2x+y+3z to 060.

5. Deliver

2x+y to 060 3x+y to 061 2x+2y to 062

6. Deliver

x+y to 060 y+z to 061 z+x to 062 2(x+y+z) to 062

7. Change (049) to 2x, (050) to 2y, (051) to 2z and send x, y and z to memory locations 060, 061, 062 respectively.

#### SEC. 4. SUBTRACTION

A complete subtraction involves three instructions; (a) transferring the minuend to rA, (b) transferring minus the subtrahend to rX, adding (rX) to (rA), and delivering the difference to rA, and (c) transferring the difference from rA to the memory.

Example 1: (049) = x, (050) = y. Deliver the difference x-y = z to 051.

Mem.

Loc. Instruction Remarks

0 20B0 49x --> rA and rXS0 50-y --> rX; x-y = z --> rA; (rX) =-y0 21C0 51

Example 2: (049) = x, (050) = y, (051) = z. Deliver the difference p = x-y to 052 and the sum q = x-y+z to rL.

Mem.

Loc. Instruction Remarks

0 20  $x \rightarrow rA$  and rXB 049 S 050 -y --> rX; x-y = p --> rA; (rX) = -y(rA) = p --> 052; (rA) = p021 Η 052 A 051 z --> rX; p+z = q --> rA; (rX) = Z(rA) = q --> rL; 0 --> rA.022 K 000

Example 3: (049) = b. It is desired to obtain -b when (a) rA is not cleared or (b) b = 0. This should be used with caution because there is a possibility of overflow depending on (rA).

Mem.

Loc. Instruction Remarks

SEC. 5. PRACTICE EXERCISES ON SUBTRACTION In the problems to follow: (049) = x, (050) = y, (051) = zprovide the instructions to:

1. Deliver

(a) x-y to 060

(b) y-x to 061

(c) y-z to 062

2. Deliver

(a) -y to 060

(b) 2x-y to 061

(c) 2x-y+z to 062

3. Deliver

(a) x-2y to 060

(b) x-2z to 061

and send y to 049, z to 050, and x to 051.

SEC. 6. MULTIPLICATION

.

| Instruct | ions                                                                                                                                                                                            |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jm       | Transfer (rX) to m; do not erase rX.                                                                                                                                                            |

| Km       | Transfer (rA) to rL; clear rA; ignore m.                                                                                                                                                        |

| Lm       | Transfer (m) to rL and rX.                                                                                                                                                                      |

| Mm       | Transfer (m) to rX; multiply (rL) by (rX) = (m);<br>deliver the rounded eleven digit product to rA;<br>(rL) unaltered.                                                                          |

| Nm       | Transfer -(m) to rX; multiply (rL) by (rX) =<br>- (m); deliver the rounded eleven digit product<br>to rA; (rL) unaltered.                                                                       |

| Pm       | Transfer (m) to rX; multiply (rL) by (rX) = (m);<br>deliver the more significant half of the twen-<br>ty-two digit unrounded product to rA, the less<br>significant half to rX; (rL) unaltered. |

The instructions M, N, and P leave three times the absolute magnitude of the multiplicand in rF.

The instructions M and N leave the less significant half of the twenty-two digit product ±50000 000000 in rX.

Register A and rX are erased before the product is delivered. Hence, products may not be automatically accumulated. The quantity having the fewer non-zero digits should be selected as the multiplier since multiplication by zeros consumes less time than multiplication by a non-zero digit.

A complete multiplication requires three instructions; (a) transferring the multiplicand to rL, (b) transferring the multiplier to rX, initiating the multiplication operation, and delivering the product to rA and rX, and (c) transferring the product from rA (and rX) to the memory.

Example 1: (049) = x, (050) = y. Deliver the eleven digit rounded product xy = z to 051.

Loc. Instruction Remarks

0 20L0 49x --> rL, and rXM0 50y --> rX; xy = z --> rA; (rL) = x0 21C0 51(rA) = z --> 051; 0 --> rA.

Example 2: (rA) = x, (050) = y. Deliver the eleven digit rounded product -xy = z to 051, leave z in rA.

Mem.

Mem.

Loc. Instruction Remarks

020K000(rA) = x --> rLN050-y --> rX; -xy = z --> rA; (rL) = x021H051(rA) = z --> 051; (rA) = z.

Example 3: (049) = L(050) = M. Deliver the twenty-two digit unrounded product P = LM to 051 and 052.

Mem.<br/>Loc.InstructionRemarks0 20L050M --> rL and rX<br/>L --> rX; LM = P --> rA and rX;<br/>(rL) = M0 21J052(rX) = less significant half of<br/>P = P s --> 052<br/C</td>C051(rA) = more significant half of<br/>P = P s --> 051.

Example 4: (049) = L, (050) = M, (051) = N. Deliver LM = P to 052 and NM = P to 053, eleven digit unrounded products are desired.

Mem.

Loc.InstructionRemarks020L050M --> rL and rXP049L --> rX; LM = P --> rA; (rL) = M021C052(rA) = P --> 052; 0 --> rAP051N --> rX; NM = P --> rA; (rL) = M022C053(rA) = P --> 053; 0 --> rA.

SEC. 7. PRACTICE EXERCISES ON MULTIPLICATION

(040) = x(041) = y(042) = Z

Write the instructions to deliver eleven digit rounded products.

```

1. (a) xy to 050

```

- (b) xz to 051

- (c) yz to 052

- (d) xyz to 053

Write the instructions to deliver eleven digit rounded products.

2. (a)  $x^2 = 050$ (b)  $-x_3 = 051$ (c)  $x^4 = 052$ (d)  $-x^5 = 053$  Write the instructions to deliver eleven digit rounded products.

- 3. (a)  $(x-y)^2$  to 050 and 051

- (b) (x-y) (x-z) to 052 and 053

- (c)  $x(y-z)^2$  to 054 and 055.

SEC. 8. DIVISION

InstructionsJmTransfer (rX) to m; do not erase rX.KmTransfer (rA) to rL; clear rA; ignore m.LmTransfer (m) to rL and rX.DmTransfer (m) to rA; divide (rA) = (m) by (rL);<br/>deliver the eleven digit rounded quotient to<br/>rA, and the eleven digit unrounded quotient to<br/>rX; (rL) unaltered.

Since all quantities, x, in the UNIVAC, must fall in the range |x| < 1, the absolute value of the dividend must be less than the absolute value of the divisor so that a proper division shall take place. If  $|Dd| \ge |Dr|$ , or if an attempt is made to divide by zero, an overflow will result (see Chapter 7).

A complete division requires three instructions; (a) transferring the divisor to rL, (b) transferring the dividend to rA and initiating the division operation, and delivering the quotient to rA and rX, (c) transferring the quotient from rA (or rX) to the memory.

Fundamental Arithmetic Operations Chapter 4 Example 1: (049) = A, (050) = B. Deliver the eleven digit rounded quotient C = A/B to 051. Mem. Loc. Instruction Remarks  $B \rightarrow rL$  and rX020 L 050 A --> rA; A/B = C --> rA; (rL) = BD 049 021 C (rA) = C --> 051; 0 --> rA.051 Example 2: (049) = A, (050) = B. Deliver the eleven digit unrounded quotient C = A/B to 051. Mem. Loc. Instruction Remarks 020 L 050  $B \rightarrow rL$  and rXA --> rA; A/B = C --> rX; (rL)=BD 049 (rX) = C --> 051.021 J 051 SEC. 9. PRACTICE EXERCISES ON DIVISION Assume that overflow will not occur in these exercises. (050) = X(051) = y(052) = ZWrite the routines to send 11 digit rounded quotients. (a)  $\frac{x}{2}$  to 060 and 061 1. (b)  $\frac{x}{y}$  to 062 (a)  $\frac{x}{7}$  to 060 2. (b)  $\frac{x}{x_{7}}$  to 061 In problem 2, also send the unrounded quotients to 062 and 063.

SEC. IO. REVIEW PRACTICE EXERCISES ON THE ARITHMETIC OPERATIONS

(050) = x(051) = y(052) = z(053) = 1

Assume that adjustments have been made so that overflow will not occur in these exercises. Write the instructions to send:

- 1.  $x^2 + 3y^2 2z$  to 060

- 2.  $(x+y)^2$  to 061

- 3. 1 + 1 + 1 + 1 = 0.062x y z

- 4.  $\frac{x^2}{y} \frac{2z}{y} \frac{y}{4}$  to 063

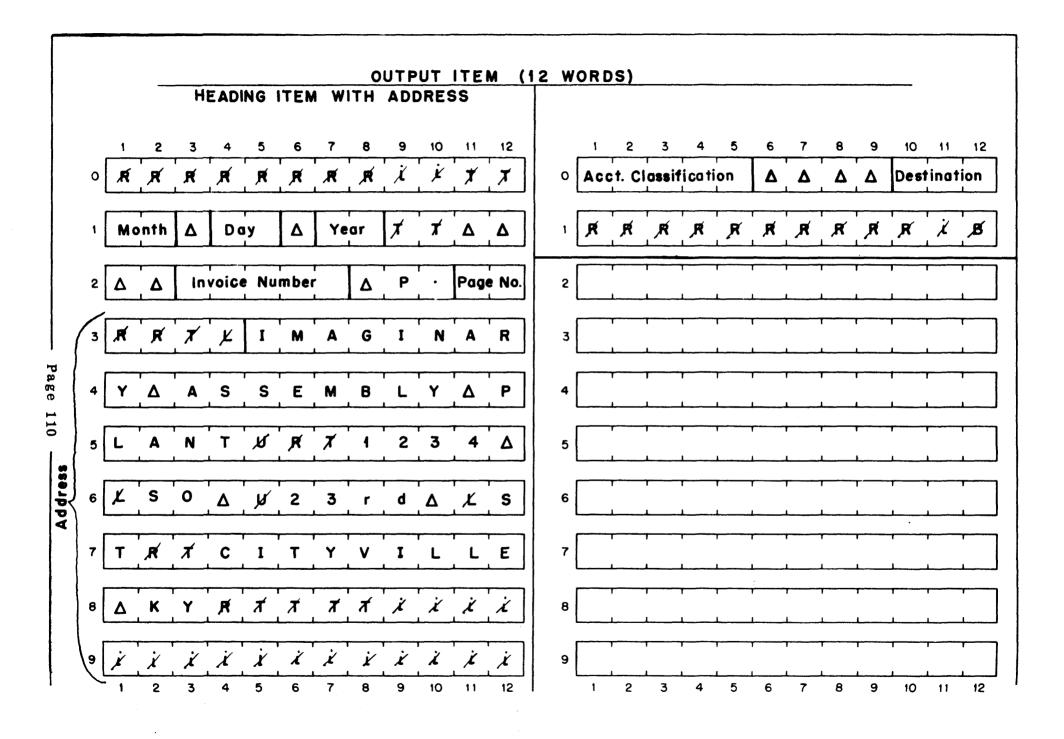

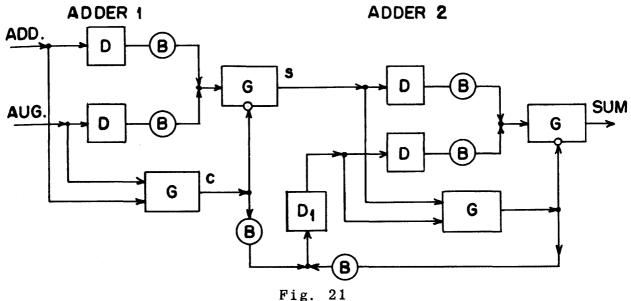

SEC. II. SPECIAL CONSIDERATION IN ARITHMETIC COMPUTATION ADDITION AND SUBTRACTION