PROGRAMMER MANUAL

BOGART - AFSAF D131

Task Number 352-7011

# NATIONAL SECURITY AGENCY Washington, 25, D. C. July 1957

# PROGRAMMER MANUAL

BOGART - AFSAF D131

Task Number 352-7011

| Compiled by: | Roy A. Carter              |         |

|--------------|----------------------------|---------|

|              | Technical Writer           | ENGR-31 |

| Reviewed by: | James A. Pederson          |         |

|              | Project Analyst            | ANEQ-1  |

|              | Vera S. Russell            |         |

|              | Project Analyst            | ENGR-13 |

| Approved by: | Harry Lofink               |         |

|              | Chief Publications Branch, | ENGR-31 |

S-87,579

# CONTENTS

|                     |       |     |       |     |   |     |   | Sec | tion - Page   |

|---------------------|-------|-----|-------|-----|---|-----|---|-----|---------------|

| INTRODUCTION .      | ۹,    | •   | •     | •   | ٠ | •   | ٥ | •   | I - 1         |

| Scope of Manual     | •     | •   | •     | ٠   | • | •   | • | ٠   | I - 1         |

| General Description | n     | •   | •     | •   | • | •   | • | •   | I - 1         |

| INTERNAL REGISTE    | RS    |     |       |     | • | •   | • | •   | II - 1        |

| Storage System      | •     | ۰   | •     | •   | • | ٠   | • | •   | II - 1        |

| Core Storage        | •     | •   | •     | • . | • | •   | • | •   | II - 1        |

| Z-Register.         |       | •   | •     | •   | • | •   | • | •   | II - 2        |

| S-Register .        | •     | •   | •     | •   | • | •   | • | •   | II - 2        |

| Arithmetic Unit     | •     |     | •     | •   | • | •   | • | •   | II - 3        |

| X-Register.         | •     | •   | . •   | •   | • | •   | • | •   | II - 3        |

| A-Register.         | ٠.    | •   | •     | •   | • | •   | ۰ | •   | II - 4        |

| Q-Register.         | •     | •   | •     | •   | • | •   | • | •   | II - 4        |

| Communication Re    | giste | ers | •     |     | • | •   | • | •   | II - 4        |

| I-Register .        | •     |     | •     | •   | • | •   | • | •   | II - 5        |

| O-Register          | • .   |     |       | •   | • | •   | • | •   | II - 5        |

| F-Register          | •     |     | •     |     | • | •   | • | •   | II - 5        |

| Internal Controls   | •     | •   | •     | •   | • | •   | • | •   | II <b>-</b> 6 |

| P-Register          | •     |     | . •   | •   |   | •   | • | •   | II <b>-</b> 6 |

| U-Register          | •     |     | •     | •   | • | •   | • | •   | III - 6       |

| B-Register          | •     |     | •     | •   | • | •   | • | •   | II - 7        |

| Sub-control Reg     | iste  | rs  | •     | •   | • | • • | • | •   | II - 8        |

| INSTRUCTIONS .      |       |     |       |     | • | •   | • |     | III - 1       |

| Definitions         |       |     | •     |     |   |     |   | •   | III - 1       |

| Instruction Code    | Fo    | rm  | at    |     |   | •   | • | •   | III - 1       |

| Arithmetic .        |       |     |       | •   | • |     |   | •   | III - 4       |

| Symbols .           |       | ٠   | •     | •   | • |     | • | •   | III - 7       |

| Mnemonic Code       |       | ۰   | •     |     |   | •   |   | •   | III - 8       |

| Instruction Term    | ms    | •   | . • • |     | ٥ | •   | • | •   | III - 11      |

| Execution Time of   | Inst  | ruc | tions |     |   |     | • | •   | III - 13      |

| Instruction Code    |       |     |       | ٠   | ٠ |     |   | ۰   | III - 16      |

| 01 ENTER B (        |       |     | •     |     |   |     | • | ۰   | III - 16      |

| 02 LOAD B (LI       |       |     |       | •   |   | •   | • | •   | III - 17      |

| 03 STORE B (S       |       |     | •     | •   |   |     | • | •   | III - 18      |

| 04 INCREASE         | •     |     | •     |     | • |     | • | •   | III - 19      |

| 05 INDEX SKIP       | •     | ,   |       |     | • | •   |   | •   | III - 20      |

| 06 THRESHOLI        |       |     |       | •   | • | •   |   | •   | III - 21      |

| 07 REPEAT (R        |       |     | •     |     | • | •   | • | •   | III - 22      |

| 11 ENTER A (E       | •     |     | •     | •   |   |     |   |     | III - 24      |

# CONTENTS

|    |    | CONTENTS                          |     |       |    |

|----|----|-----------------------------------|-----|-------|----|

|    |    |                                   |     |       |    |

| ė. | 12 | LOAD A (LDA)                      | J   | (II - | 25 |

| •  | 13 | STORE A (STA)                     | I   | Щ -   | 26 |

|    | 14 | COMPLEMENT A (COA)                | 1   | III - | 27 |

|    | 15 | SHIFT A (SHA)                     | . ] | ui -  | 28 |

|    | 16 | LONG SHIFT (LSH)                  | ]   | UI -  | 29 |

|    | 17 | A JUMP (AJP)                      | J   | III - | 30 |

|    | 21 | ENTER Q (ENQ)                     | ]   | III - | 32 |

|    | 22 | LOAD Q (LDQ)                      | ]   | III - | 33 |

|    | 23 | STORE Q (STQ)                     | ]   | III - | 34 |

|    | 24 |                                   | ]   | ui -  | 35 |

|    | 25 | SHIFT Q (SHQ)                     | ]   | ui -  | 36 |

|    | 26 | TRANSFER A TO Q (TAQ)             | ]   | ui -  | 37 |

|    | 27 | Q JUMP (QJP)                      | ]   | III - | 38 |

|    | 31 | ADD CONSTANT (ADC)                | ]   | III - | 40 |

|    | 32 | ADD (ADD)                         | ]   | III - | 41 |

|    | 33 | ADD REPLACE (ADR)                 | 3   | III - | 42 |

|    | 34 | REPLACE ADD ONE (RAO)             | . ] | III - | 43 |

|    | 35 | LOAD A, ADD Q (LAQ)               |     | Ш -   | 44 |

|    | 36 | ADD Q AND STORE (AQS)             | ]   | III - | 45 |

|    | 37 | REPLACE ADD Q (RAQ)               | 3   | Ш-    | 46 |

| •  | 41 | SUBTRACT CONSTANT (SBC)           | 1   | III - | 47 |

| •  | 42 | SUBTRACT (SUB)                    | 1   | III - | 48 |

| •  | 43 | SUBTRACT REPLACE (SBR)            | ]   | III - | 49 |

| •  | 44 | REPLACE SUBTRACT ONE (RSO)        | 1   | III - | 50 |

| •  | 45 | LOAD A, SUBTRACT Q (LSQ)          | ]   | ШI -  | 51 |

| •  | 46 | SUBTRACT Q AND STORE (SQS)        | 7   | III - | 52 |

| •  | 47 | REPLACE; SUBTRACT Q (RSQ)         | J   | III - | 53 |

| ,  | 50 | LOGICAL PRODUCT (LPR)             | ]   | III - | 54 |

|    | 51 | ADD LOGICAL PRODUCT (ALP)         | · ] | III - | 55 |

|    | 52 | SELECTIVE COMPLEMENT (SCO)        | ,   | III - | 56 |

|    | 53 | SUBSTITUTE BITS (SBT)             | ]   | ni -  | 57 |

|    | 54 | REPLACE LOGICAL PRODUCT (RLP)     | ]   | III - | 58 |

|    | 55 | REPLACE ADD LOGICAL PRODUCT (RAL) | ]   | III - | 59 |

|    | 56 | REPLACE SELECTIVE COMPLEMENT (RSC | ) 1 | III - | 60 |

|    | 57 | REPLACE SUBSTITUTE BITS (RSB)     | ]   | ui -  | 61 |

| 4  | 60 | MULTIPLY STEP (MUL)               | ]   | III - | 62 |

| 4  | 61 | DIVIDE STEP (DIV)                 | ]   | III - | 66 |

| I  | 62 | SELECTIVE CLEAR (SCL)             | J   | III - | 70 |

| •  | 64 | EQUAL SKIP (ESK)                  | ]   | III - | 71 |

|    | 65 | UNEQUAL SKIP (USK)                | ]   | ш -   | 72 |

| 1  | 66 | GREATER SKIP (GSK)                | J   | III - | 73 |

|    |    | LESS SKIP (LSK)                   | 1   | TTT _ | 74 |

# CONTENTS

|     | 70      | EXTER     | NAL FU  | JNCT   | ION -      | (EXI  | r)    | •          | •    | i 1<br>• | III | - | 75 |

|-----|---------|-----------|---------|--------|------------|-------|-------|------------|------|----------|-----|---|----|

|     | 71      | INPUT     | (INP)   | •      | •          | •     | •     |            |      |          | III | - | 76 |

|     | 72      | OUTPU     | r (out  | ) .    | •          |       |       | •          | •    | •        | III | _ | 78 |

|     | 73      | TRACE     | JUMP    | (TRJ   | ) .        | •     | •     | •          | •    |          | III | _ | 80 |

|     | 74      | SENSE 3   | JUMP (  | (SNJ)  | •          | •     | •     | •          | •    | •        | III | - | 81 |

|     | 75      | SELECT    | CIVE JU | JMP    | (SLJ)      | •     | •     | •          | •    | •        | III | - | 83 |

|     | 76      | SELECT    | CIVE SI | OP     | (SLS)      | ٠     |       |            | 6    |          |     |   |    |

| EX  | TERN.   | AL FUN    | CTION   | CODI   | <b>E</b> S | •     | •     | , <b>•</b> | •    | •        | IV  | - | 1  |

|     | List o  | f Externa | al Func | tion ( | Codes      | •     | •     | •          | •    |          | IV  | - | 1  |

|     | Descr   | iption of | Extern  | al Fu  | nctio      | n Co  | des   | • ,        | •    | •        | IV  | - | 5  |

| OP  | ERAT    | ING PRO   | CEDUF   | RES    | •          | •     | •     | •          | •    | •        | V.  |   | 1  |

|     | Contro  | ol Panel  |         | •      | •          | •     | •     | •          | •    | •        | V   | - | 1  |

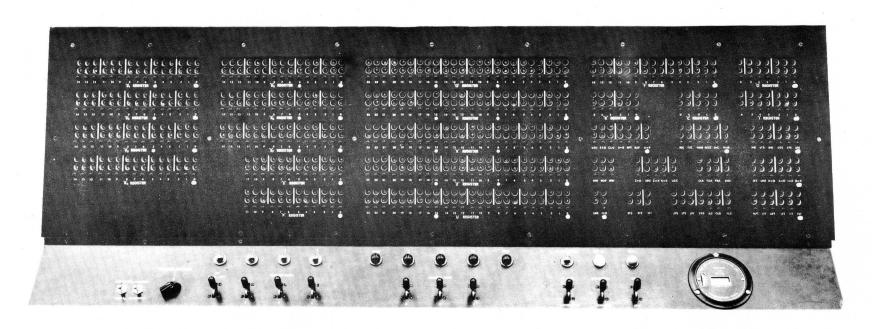

|     | Indica  | tor Displ | lay and | Main   | tenar      | ice F | anel  | •          | •    | •        | V   | - | 5  |

|     | Progr   | am Load   | Mode    | •      | •          | •     | •     | •          | •    | •        |     |   |    |

|     | Startin | ng Opera  | tion    | •      | . •        | •     | •     | •          | •    | •        | V   | - | 7  |

| ILI | LUSTR   | ATIONS    | (Foll   | lowin  | g pag      | es li | isted | )          |      |          |     |   |    |

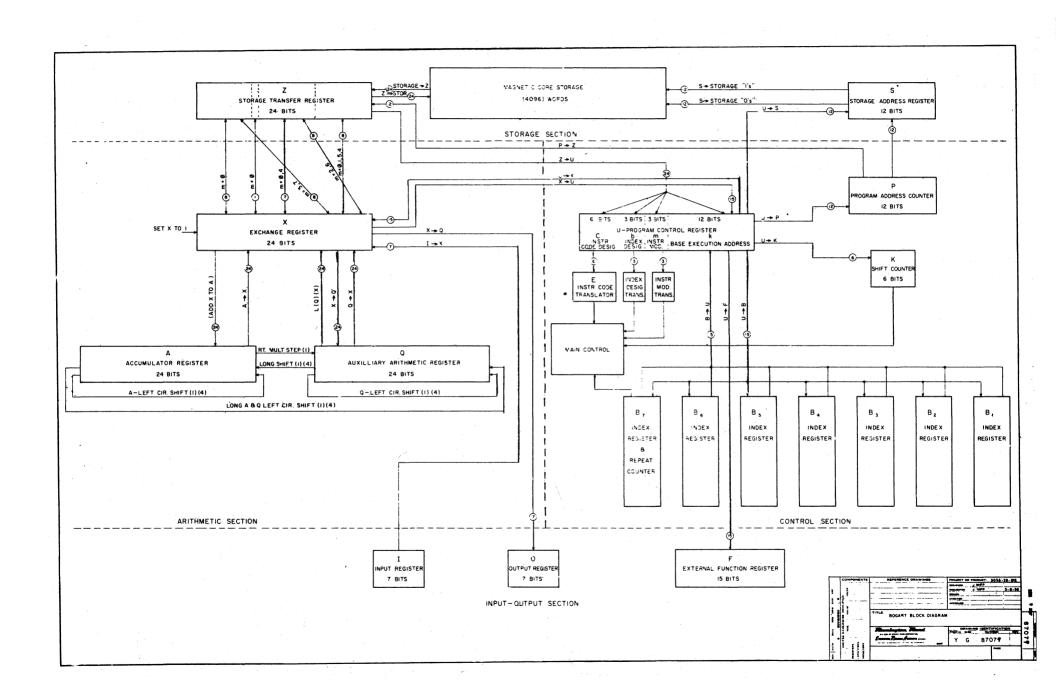

|     |         | RT CON    |         |        |            |       | •     |            |      | •        | I   | _ | 1  |

|     |         | K DIAGR   |         |        |            |       |       |            |      |          |     |   |    |

|     | DISPL   | AY PAN    | EL DIA  | GRA    | M          | •     | •     | •          | •    |          | II  | - | 9  |

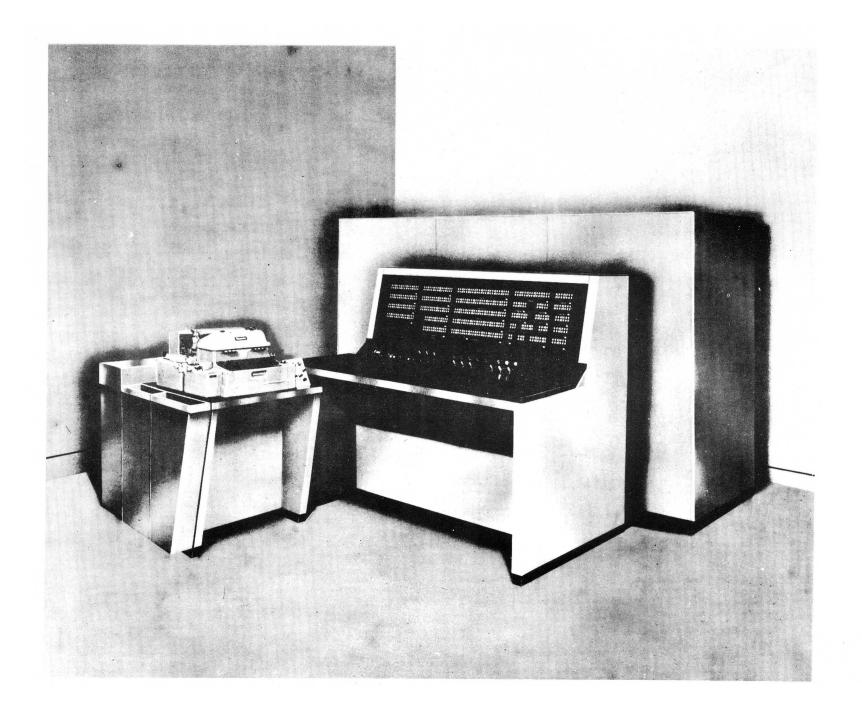

|     | DISPL   | AY AND    | CONT    | ROL    | PANI       | ar. E | тон   | OGE        | HGAS | 1,1      | īV  | _ | 16 |

#### BOGART

#### PROGRAMMERS MANUAL

#### SECTION I

#### INTRODUCTION

#### A. Scope of Manual

This manual is a guide for BOGART programmers and operators. It may also be used as a training supplement for new persons in the computer field.

The properties and description of internal registers are presented to give the reader a basic knowledge of the logical design of BOGART. The relationship between the computer and peripheral equipment is detailed to demonstrate the technical aspects of computer applications. The last section describes the operating procedures of BOGART.

#### B. General Description

BOGART is a general-purpose computer using a modified one-address instruction code. It has a 4096-word magnetic-core storage. Special commands enable BOGART to operate on a 24-bit word, as a whole, or any 8-bit third of a word. The functions of this computer include manipulating data, differentiating various forms of data, performing analytical operations, counting operations, and arithmetic operations. The specific operations are determined by a program.

The computation speed of BOGART is comparable to that of ATLAS and ABNER. Physically, however, BOGART is much smaller than either of these computers. The main cabinet is 8 feet long, 3 feet wide, and 5 feet high. External equipment provides input and output. The inputs are punched paper tape, Flexowriter, punched cards, and magnetic tape. Output is available through the same media as input with the addition of a line printer. BOGART also has an external motor-alternator unit which supplies 208-volt, 3-phase, 400-cycle alternating current. This is the main power source for the computer.

#### BOGART

#### PROGRAMMERS MANUAL

#### SECTION II

#### INTERNAL REGISTERS

#### A. Storage System

The basic unit of information in BOGART is the 24-bit binary word. It may be interpreted by the various registers of the machine as a positive or negative number, an instruction, a constant, or as three units of 8-bit data. This information may be stored in the storage section for any length of time and recalled or replaced when desired by the program. The storage section consists of the core storage, the Z-register, and the S-register.

#### 1. Core Storage

This storage can retain 4096 24-bit words, a total of 98,304 bits of information.

The magnetic-core storage contains 24 planes. Each 10-inch plane is a 64 by 64 square array of 4096 cores. Three of the four wires running through each core write information into the core and the fourth wire senses whether a 1 or a 0 is stored in the core.

If the core is magnetized in one direction, a l is stored in it; and if it is magnetized in the reverse direction, a 0 is stored in it. Information read out by applying a current to the two read-out wires drives the core into its zero state. If a l is stored in the core, the magnetic direction-change induces a voltage in the read-out wire. By sensing the voltage on the read-out wire, it is possible to determine the previous magnetic state of the core.

Since the read-out wire sets a core to the zero state, it is necessary for the memory circuits to restore the core to a one-state. If it contains a l, this is the regeneration portion of the storage cycle. The total storage cycle of read-out and information regeneration takes 20 microseconds per word. The information

stored in any location is available to the Z-register in approximately 8 microseconds of the cycle. While the storage control is restoring the information in the core, the computer takes this information and processes it in the machine register.

Each plane in the magnetic-core storage corresponds to one bit of a word in the memory; and the 24 planes store a complete word. Each core in the plane corresponds to one of the 4096 storage locations. To select a word in the storage, the storage control accepts the address stored in the S-register. The interpreted address supplies one of the 64 horizontal read-out windings and one of the 64 vertical read-out windings of the storage matrix with half of the current necessary to change the magnetic state of a core. Only the core at the intersection of the two windings receiving full current, switches. This action induces a read-out voltage on the read-out winding of each core-storage plane. All other cores receive a half current. These cores do not switch and are not read out.

Information is stored in the core storage by the same procedure as in read-out. When the information in a set of cores has been read out, the information is not used for regeneration, but the core is used for new information.

#### 2. Z-Register

This register is the communication link between the magnetic-core storage and the internal registers of the computer. The Z-register, a 24-bit register, receives information that is read from the magnetic cores and holds the information for regeneration. The Z-register also receives information from the X- and P-registers and holds it to be stored in the magnetic cores.

#### 3. S-Register

This register is the storage address register for the core storage. The S-register retains the address of the storage location that is to be referred to by the program. It specifies which corestorage location is to be read into the Z-register and at which location the information contained in the Z-register is to be stored in the core storage.

The S-register receives address information from the P-register and the K-portion of the U-register.

#### B. Arithmetic Unit

This unit consists of the exchange or X-register, the accumulator or A-register, and the auxiliary arithmetic or Q-register. By the appropriate operation of these registers it is possible to perform addition, subtraction, multiplication, and division. It is also possible for the control to make decisions based on the contents of the A- or the Q-registers. The bit positions of all registers are numbered 23 to 0, from left to right. Arithmetic is performed on the one's-complement arithmetic system. Negative numbers are represented by the one's complement of the positive number. Each digit of the number is reversed to find its negative. Thus, for an eight-bit word, plus five is 00000101, minus five is 11111010.

#### 1. X-Register

This register is a 24-bit register with several special exchange functions. It transfers information between the A-register, Q-register, U-register, I-register, and O-register. The X-register, the major exchange unit of the arithmetic unit, has the following properties:

- a. The complement of the contents of the X-register may be transferred to A or Q. In complementing, the value of each bit of the register is reversed. A one becomes a zero and a zero becomes a one. This form of complementing enables the X-register to change the sign of a number, therefore subtraction is essentially a case of complementing and adding.

- b. The X-register may receive the logical product of the Q- and X-registers. In the logical product, the X-register contains a one in each bit position of the Q-register which contained a one.

- c. An 8-bit number may be extended to become a signed 24-bit number. This is a function of the transmission from Z to X. The repositioning of a number while it is being transmitted from Z to X causes an 8-bit number to be stored in bits 7 to 0 of the X-register. During the transmission of the 8-bit number, the leftmost bit is examined and if it is a one, bits 23 to 8 of X are made all ones. If the left-most bit is a zero, bits 23 to 8 of X are left in the zero state.

- d. The X-register receives a full 24-bit word from the A-, the Q-, or the Z-registers. The X-register can transmit a full 24-bit word to the A-, the Q-, or the Z-registers.

- e. The X-register may receive a 7-bit character from the I-register (input) for storage in the core storage. The X-register may send 7-bit characters (6 to 0) to the O-register (output) for operation of the output equipment. A portion of a word may be transmitted to or from bits 7 0, or 14 0 of the X-register as follows:

| X-R | egi | st | er | B | its |    | Tć | or  | From       | Registe |

|-----|-----|----|----|---|-----|----|----|-----|------------|---------|

|     | 7   | _  | 0  |   |     |    |    | 7   | - 0        | Z       |

|     | 7   | _  | 0  |   |     |    |    | 15  | - 8        | Z       |

|     | 7   | _  | 0  |   |     | •, | •  | 23  | - 16       | Z       |

|     | 14  | -  | 0  |   |     |    |    | 14  | <b>-</b> 0 | Z       |

| **  | 1.4 |    | Λ  |   |     |    |    | 1.4 | ^          | * *     |

# 2. A-Register

This 24-bit register is the accumulator of the BOGART arithmetic unit. The contents of the X-register are added to the A-register. It can be cleared to all zeros on command. It shifts circularly. In the multiply and divide step, the shifting functions are different and are covered in the instruction code.

#### 3. Q-Register

This register is a 24-bit auxiliary arithmetic register. It is used with the A-register in the MULTIPLY and DIVIDE STEP instructions and may be used to form a logical product. Several other functions of the Q-register are defined in the instruction code. The Q-register transmits or receives information from the X-register. It has left circular shifting properties and may be combined with the A-register as a 48-bit register.

The Q-register acts as an assembly or buffer register for various types of input and output as defined in the instruction code.

#### C. Communication Registers

These registers of BOGART translate internal computer signals into a form suitable for activating the external device. The standard

communications signal between the computer and the external equipment has sufficient voltage to saturate a direct-coupled transistor. The output register and the external-function register change the timed pulses from the computer to a direct-current signal. The input register changes a direct-current signal to the clocked pulses necessary for internal use in the computer.

#### 1. I-Register

The input register is the information source for the computer. If a high-speed information source is selected, the input register requests information from that source whenever an input instruction appears in the control unit. If a slow-speed source is selected (punched paper tape unit), one frame is read in anticipation of the input instruction that follows. When an input instruction appears in control, the information read into the I-register is transmitted to the memory unit of the computer. After information is taken from the I-register, the computer cannot use the I-register until new information has been read into it.

#### 2. O-Register

The output register is the principal information output of the X-register. When information is placed in the O-register, control sends signals to the external equipment causing it to accept this information. After the external equipment has accepted the information and is ready for more, it returns a signal to the BOGART control which then may cause more information to be transmitted from the X-register to the O-register.

# 3. F-Register

This register is the external-function register of the computer. When an external-function instruction appears in control, the F-register receives a 15-bit coding from the low-order 15 bits of the U-register.

All of the external units to the computer monitor the F-register. After information enters the F-register, BOGART control emits a signal on the external function-enable line. This signal causes all external control lines to examine the F-register content.

When an external unit finds a pertinent function in the F-register, this unit performs the function and sends back an external function resume-signal to inform the computer that the external function has been performed. The return-time of the function-resume signal depends on the external function performed.

#### D. Internal Controls

This control unit obtains instructions from the memory, interprets them, and operates the other BOGART registers and units in correct sequence to initiate the specified instructions. It consists of a series of registers with functions as defined below:

#### 1. P-Register

This 12-bit register always specifies the memory location which contains the next instruction. In the normal operation, successive instructions are obtained from successive memory locations.

To allow for the use of the NORMAL JUMP instruction, P may also receive a 12-bit number from bits 11 to 0 of the U-register. P transmits information to the S-register and also transmits its contents to the Z-register when the RETURN JUMP instruction is activated.

#### 2. U-Register

The U-register is the principal control register of the computer. It consists of 24-bits of storage which may be numbered 23 to 0, from left to right. Various portions of the U-register have different functions. Bits 23 to 18 are interpreted as the operation code and the binary pattern of these bits identifies the instruction to be performed by the computer. In the block diagram, these six bits are called "E". They may be transmitted to the instruction-code or egister.

Bits 17 to 15, called "b", specify which of the seven Bregisters will be added to bits 14 to 0 of the U-register before the

<sup>1</sup> See SectionV, EXTERNAL COMMUNICATION SYSTEM, for details of the external functions and codes.

instruction is executed. Bits 17 to 15 of U are transmitted to the three-bit T-register. This register performs the translation and decides which of the B-registers is referred to.

Bits 14 to 12 of U, called "m", specify the modification of the portion of a word to be handled in transmissions from X to Z and Z to X. It is also used to specify variations in the Stop and Jump type instructions.

Bits 11 to 0 of U, called "k", specify a memory reference. These bits may be transmitted to the S-register in the storage control unit.

Bits 14 to 0 of U may be transmitted to bits 14 to 0 of the X-register. This is used in certain orders which use only constants up to 77777.

The U-register receives 24-bits of information from the Z-register in the storage unit. Since the U-register does not depend on the X-register in the Arithmetic unit, they can operate simultaneously.

The low-order 15 bits of U may also receive information from the specified B-boxes.

The low-order 12 bits of U are transmitted to the S-register to specify a memory reference in executing a NORMAL instruction. These same 12 bits may be transmitted to the P-register for executing a JUMP instruction.

The right-most 15 bits of U may be transmitted to the F-register for communication with external equipment. The 15 bits may be transmitted to the X-register where they are treated as a 15-bit positive quantity in the type of instruction that uses the lower 15-bits as a constant.

#### 3. B-Registers

The control unit of BOGART has seven 15-bit B-registers. Each may receive information from the low-order 15 bits of the U-register. The contents of any B-register may be added to the low-order 15 bits of an instruction in the U-register before the instruction is executed by control. The B-register to be used is

decided by the value of the T-register which receives its information from bits 17 to 15 of the U-register.

Instructions are available that add a constant to the B-register specified, compare the B-register with a specified constant, and allow the program to take different courses, depending on the relative magnitude of the B-register.

Addition of the B-register contents to the lower 15 bits of the U-register occurs modulo  $2_1^{15}$ . The carry that may leave the left-most bit of the U addition is ignored. The B-registers may be used to subtract a constant from the specified address of an instruction. By placing the two's complement (one more than the one's complement) of the minuend in the B - register.

The  $B_7$ -register is available as the repeat counter in addition to its normal use as a B-register. In the REPEAT instructions, the repeat count is stored in  $B_7$  and counted down by one each time the repeated instruction is performed. If the repeated instruction calls for a skip or a jump of program address, the content of the  $B_7$ -register is left in  $B_7$  and the jump or skip occurs. This feature is discussed under programming.

#### 4. Sub-control Registers

The sub-control units of BOGART are the N-, E-, and K-registers. They are discussed briefly because they may be of interest to the programmer.

#### a. N-Main Control

This unit controls normal information recirculation and transmission throughout the computer. All computer subcommands are controlled transmissions of information from one register to another. Any instruction may be performed by setting up the correct pattern of sub-commands.

#### b. E-Instruction Code Translator

The left six bits of U are transmitted to the E-cores which decode the instruction code (c) to one of 57 possible machine operations. The E-cores interpret the command code and set up the correct sequence of sub-commands in Main Control that enables the computer to execute the designated instructions.

# c. K-Register

This six-bit register is a counter. It obtains its data from the low-order six bits of U which is the shift count. As a shift is executed, the K-register is counted down to zero. At zero the shift is completed and the next instruction is initiated.

#### BOGART

#### PROGRAMMERS MANUAL

#### SECTION III

#### INSTRUCTIONS

#### A. Definitions

#### 1. Instruction Code Format

The program control register interprets a 24-bit instruction for program operation. The bits are numbered from left to right in descending order, 23, 22, 21 . . . . 2, 1, 0. This 24-bit sequence is divided into designator sections (c, b, m, and k), each with its specific purpose.

Designator Section

Number of Bits

| С | ъ | m | k  |

|---|---|---|----|

| 6 | 3 | 3 | 12 |

Figure 1

#### a. c-Designator

This 6-bit function code, represented by bits 23 to 18 of the instruction, specified one of 57 possible instructions to be executed by the program control section. The instruction code is listed on page III-16.

#### b. b-Designator

The program control section contains seven 15-bit B-boxes, also called index registers. Each B-box stores a constant which may be used to modify the quantities m and k (the 15 low-order bits of an instruction; bits 14 to 0). After the instruction appears in the control unit, m and k are modified by the specified B-box prior to the execution of the instruction. The modified instruction appears only in the U-register, but the original instruction in the storage is unchanged. Though not physically present, B-box zero may be considered to be a 15-bit register whose content is always zero.

The 3-bit index designator, b, is represented by bits 17 to 15 of the instruction. These bits select the appropriate B-box according to the following assignments.

|   | 0             | Q           |                                |

|---|---------------|-------------|--------------------------------|

| 0 |               | Make no mod | lification of m, k             |

| 1 |               | Add to m, k | the contents of B <sub>1</sub> |

| 2 |               | Add to m, k | the contents of B2             |

| 3 | • • • • • • • | Add to m, k | the contents of B <sub>3</sub> |

| 4 |               | Add to m, k | the contents of B <sub>4</sub> |

| 5 |               | Add to m, k | the contents of B <sub>5</sub> |

| 6 |               | Add to m, k | the contents of B <sub>6</sub> |

| 7 |               | Add to m, k | the contents of B7             |

Assignment

Although B<sub>7</sub> is available as a modifier, it is permanently wired as a counter for the REPEAT instruction. When a REPEAT instruction occurs, the previous content of B<sub>7</sub> is eradicated. B<sub>7</sub> then assumes the value of the address-portion make the REPEAT instruction.

The same B-box may be used to modify any number of instructions in a program cycle.

#### c. m-Designator

b-Designator

The modifier, m, is represented by bits 14 to 12 of every instruction. The modifier enables BOGART to operate on a 24-bit word, an 8-bit third of a word, or the low-order 15 bits of a word. An 8-bit third of a word is limited to low-order, center, or high-order segments. The low-order 8 bits are bits 7 to 0; the center 8 bits are 15 to 8; and the high-order 8 bits are 23 to 16.

| Modifier |   |   |   |   | C | orı | espo | ond | ing | Bits |

|----------|---|---|---|---|---|-----|------|-----|-----|------|

| 0        | • | ۰ | ۰ |   | ٠ |     | 23   | to  | 0   |      |

| 1,5      |   | ٠ |   | ٠ |   |     | 7    | to  | 0   |      |

| 2,6      |   | ۰ | • | ۰ |   |     | 15   | to  | 8   |      |

| 3, 7     |   | ۰ |   |   |   |     | 23   | to  | 16  |      |

| 4        |   |   |   |   |   |     | 14   | to  | 0   |      |

The instructions given by these values are:

- m 0 Operate on the entire 24-bit word as stored.

- m 1 Operate on a 24-bit word which has the loworder 8 bits corresponding to the low-order 8 bits of the word in storage, and which has the high-order 16 bits equal to the eighth bit.

- m 2 Operate on a 24-bit word which has the loworder 8 bits corresponding to the center 8 bits of the word stored;, and which has the high-order 16 bits equal to the eighth bit.

- m 3 Operate on a 24-bit word which has the loworder 8 bits corresponding to the high-order 8 bits of the word in storage, and which has the high-order 16 bits equal to the eighth bit.

- m 4 Operate on a 24-bit word which has the loworder 15 bits corresponding to the low-order 15-bits of storage, and which has the high-order y bits equal to zero.

- m 5 Operate on a 24-bit word which has the low-order 8 bits corresponding to the low-order 8 bits of the word in storage, and which has the high-order 16 bits equal to zero.

- m 6 Operate on a 24-bit word which has the loworder 8 bits corresponding to the center 8 bits of the word in storage, and which has the high-order 16 bits equal to zero.

- m 7 Operate on a 24-bit word which has the loworder 8 bits corresponding to the high-order 8 bits of the word in storage, and the highorder 16 bits equal to zero.

When an 8-bit third of a word is used in the 24-bit arithmetic registers of BOGART, the 8 bits are relocated to occupy bit-positions 7 to 0 of the register. The high-order 16 bits of the register assume the value specified by m. In storing with m=1, 2, 3, 5, 6, and 7, BOGART replaces the specified third of a word with bits 7 to 0 of the arithmetic register.

When m = 4, bits 14 to 0 of the original word occupy the same bit-positions in the arithmetic registers. The remaining positions in the register, bits 23 to 15, are zeros. In storing with m = 4, BOGART replaces bits 14 to 0 of the stored word with the corresponding bits of the arithmetic register. The remaining bits of the word are unchanged.

#### d. k-Base Execution Address

The 12-bit base execution address, k, as modified by B, specifies one of the 4,096 storage addresses as the location of the operand used in the execution of the instruction. Designator k is represented by bits 11 to 0 of the instruction.

#### 2. Arithmetic

Minus zero, or all ones, causes some programming trouble in the one's complement system. Minus zero is considered a negative number for POSITIVE and NEGATIVE JUMP, but for ZERO and NONZERO JUMP it is considered not zero. Usually BOGART will not generate a minus zero with normal arithmetical operations, but in certain cases a minus zero may be generated in the accumulator. Orders LPR, RLP, SCO, RSC, SBT, and LSH may or may not generate a minus zero in the accumulator.

Examples of one's complement arithmetic with word size = 12 are to be found on pages III - 5 and III - 6.

#### ADDITION:

SUBTRACTION: The subtrahend is complemented, then added to the minuend.

| Decimal            | Octal              | One's Complement                                                                                                             |

|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------|

| +7                 | +7                 | 00000000111                                                                                                                  |

| (-) -5             | (-) -5             | 00000000101 (complement of -5)                                                                                               |

| +12                | +14                | 00000001100 (answer +14)                                                                                                     |

| -7                 | -7                 | 111111111000                                                                                                                 |

| (-) -6             | (-) -6             | 000000000110 (complement of -6)                                                                                              |

| -1                 | -1                 | 111111111110 (answer -1)                                                                                                     |

| +3                 | +3                 | 00000000011                                                                                                                  |

| (-) -4             | (-) -4             | 00000000100 (complement of -4)                                                                                               |

| +7                 | +7                 | 00000000111 (answer +7)                                                                                                      |

| -2<br>(-) +5<br>-7 | -2<br>(-) +5<br>-7 | carry 111111111101<br>(-) 1111111111010 (complement of +5)<br>(1) 111111110111<br>1 (add carry)<br>1111111111000 (answer -7) |

#### 3. Symbols

- - (arrow) transmit

- () (parenthesis) content of

- (prime) complement of

- (+) (circular plus) add without carry

- > greater than, A > B (A is greater than B.)

- < -less than, A < B (A is less than B.)

- .. therefore

- 🦈 return jump

- normal jump

- (on) status of switch; control light corresponding to switch.. ON

- (off) status of switch; control light corresponding to switch.. OFF

- Y low-order 15 bits of instruction after modification by B

- y low-order 15 bits of instruction without modification by B

- (Y) content of storage location specified by Y

- JS jump switch

- SS stop switch

- Q<sub>23</sub> (subscript <sub>23</sub>) the 24th or left-most bit position of the register

- Ao (subscript o) the right-most bit of the accumulator

$A_n$  - (subscript  $_n$ ) the corresponding bit position (0 through 23) of the accumulator

NI - next instruction

$(A_s)$  - (subscript  $_s$ ) the shifted content of the accumulator

(A<sub>i</sub>) - (subscript i) the initial content of the accumulator

$(A_f)$  - (subscript f) the final content of the accumulator

L(Q)(Y) - logical (bit by bit) product of (Q) and (Y)

#### 4. Mnemonic Code

Mnemonic is defined as an aid to memory. The following pages list the octal code, mnemonic code, name of instructions, and the symbolic description for each instruction in BOGART. The mnemonic code has been chosen as a standard notation in refering to BOGART instructions.

| Octal<br>Code | Mnemonic<br>Code | Instruction    | Symbolic Description of the Instruction                                |

|---------------|------------------|----------------|------------------------------------------------------------------------|

| 00            |                  |                |                                                                        |

| 01            | ENB              | Enter B        | y → B                                                                  |

| 02            | LDB              | Load B         | $(Y) \rightarrow B$                                                    |

| 03            | STB              | Store B        | (B) → Y                                                                |

| 04            | INB              | Increase B     | $(B)_i + y \rightarrow B_f$                                            |

| 05            | BSK              | Index skip     | If (B) > y, skip and clear B;<br>if (B) < y, (B) + $1 \rightarrow B_f$ |

| 06            | TSK              | Threshold skip | If $(B) > y$ , skip                                                    |

| 07            | RPT              | Repeat         | Do next instruction Y times                                            |

| 10            |                  | Unassigned     |                                                                        |

| 11            | ENA              | Enter A        | $Y \rightarrow A$                                                      |

| 12            | LDA              | Load A         | (Y) ->A                                                                |

| 13            | STA              | Store A        | (A) → Y                                                                |

| 14            | COA              | Complement A   | (A') ->-A                                                              |

| 15            | SHA              | Shift A        | $(A)_{s} \rightarrow (A)_{f}$                                          |

| 16            | LSH              | Long shift     | $(A, Q)_S \rightarrow (A, Q)_f$                                        |

| 17            | AJP              | A jump         | (See symbolic expression for each option on page III-30.)              |

| Octal<br>Code                                | Mnemonic<br>Code                              | Instruction                                                                   | Symbolic Description of the Instruction                                                                                                                                   |

|----------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27 | ENQ<br>LDQ<br>STQ<br>COQ<br>SHQ<br>TAQ<br>QJP | Unassigned Enter Q Load Q Store Q Complement Q Shift Q Transmit A to Q Q jump | $(Q_s) \rightarrow Q_f$                                                                                                                                                   |

| 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37 | ADC<br>ADD<br>ADR<br>RAO<br>LAQ<br>AQS<br>RAQ | Add replace<br>Replace add one<br>Load A, add Q                               |                                                                                                                                                                           |

| 40<br>41<br>42<br>43<br>44                   | SBC<br>SUB<br>SBR<br>RSO                      | Replace subtract one                                                          | $(A)_{i} - Y \longrightarrow A_{f}$ $(A)_{i} - (Y) \longrightarrow A_{f}$ $(A)_{i} - (Y) \longrightarrow A_{f} \text{ and } Y$ $(Y) - 1 \longrightarrow A \text{ and } Y$ |

| 45<br>46<br>47                               | LSQ<br>SQS<br>RSQ                             | Load A, subtract Q Subtract Q and store Replace subtract Q                    | $(Y) - (Q) \longrightarrow A$<br>$(A)_i - (Q) \longrightarrow A_f \text{ and } Y$<br>$(Y) - (Q) \longrightarrow A \text{ and } Y$                                         |

| 50<br>51<br>52                               | LPR<br>ALP<br>SCO                             | Logical product Add logical product Selective                                 | $L(Q)(Y) \rightarrow A$ $(A)_i + L(Q)(Y) \rightarrow A_f$                                                                                                                 |

| 53<br>54                                     | SBT .<br>RLP                                  | complement Substitute bits Replace logical product                            | If $(Y)_n = 1$ , complement $(A)_n$<br>$L(Y_n)(Q_n) + L(A_n)(Q_n) \longrightarrow A_f$<br>$L(Q)(Y) \longrightarrow A$ and $Y$                                             |

| Octal<br>Code | Mnemonic<br>Code | Instruction       | Symbolic Description of the Instruction                         |

|---------------|------------------|-------------------|-----------------------------------------------------------------|

| 55            | RAL              | Replace add logi- |                                                                 |

|               |                  | cal product       | $(A)_i + L(Q)(Y) \rightarrow A \text{ and } Y$                  |

| 56            | RSC              | Replace selective |                                                                 |

|               |                  | complement        | If $(Y)_n = 1$ , complement $(A_n)$ , $A_n \longrightarrow Y_n$ |

| 57            | RSB              | Replace           |                                                                 |

|               |                  | substitute bits   | $L(Y_n)(Q_n) + L(A_n)(Q'_n) \rightarrow A_n$<br>and $Y_n$       |

| 60            | MUL              | Multiply step     | Product→Q                                                       |

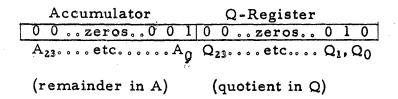

| 61            | DIV              | Divide step       | Quotient - Q, remainder - A                                     |

| 62            | SCL              | Selective clear   | $(A)_i + L(A)(Y) \rightarrow A_f$                               |

| 63            | •                | Unassigned        |                                                                 |

| 64            | ESK              | Equal skip        | If $(A) = (Y)$ , skip                                           |

| 65            | USK              | Unequal skip      | If $(A) \neq (Y)$ . skip                                        |

| 66            | GSK              | Greater skip      | If $(A) > (Y)$ , skip                                           |

| 67            | LSK              | Less skip         | If $(A) < (Y)$ , skip                                           |

| 70            | EXF              | External function | Y F                                                             |

| 71            | INF              | Input             | If $m = 1, 2, 3, 5, 6$ or $7$ ; $I \rightarrow Y$               |

| 72            | OUT              | Output            | If $m = 1, 2, 3, 5, 6 \text{ or } 7; Y \rightarrow O$           |

| 73            | TRJ              | Trace jump        |                                                                 |

| 74            | SNJ              | Sense jump        | (See section III-C for descrip-                                 |

| 75            | SLJ              | Selective jump    | tion and symbolic expression                                    |

| 76            | SLS              | Selective stop    | for each option.)                                               |

| 77            | •                | Unassigned        |                                                                 |

The format for the following Instruction Codes and Command Steps was selected as the most practical adaptation of this material.

#### 5. Instruction Terms

#### a. RETURN JUMP

Transmit the address of the next sequential instruction to the low-order 15 bits of the storage location specified by the low-order 12 bits of the RETURN JUMP instruction. Then change the program address to obtain the next instruction from the storage location specified plus one.

The "b"-modifier may be used.

The third-of-a-word feature may not be used.

The repeat may be used. The repeat sequence is terminated after the execution of a Jump instruction when the jump occurs, storing the number of unperformed repetitions in B<sub>7</sub>. If the Jump instruction does not occur, repetition of the instruction continues.

The RETURN JUMP is very useful for sub-routines.

### Example:

Main Program

ML

OP

B

M

Address

X

SLJ

4,5,6 or 7

Y

X+1

I

I

I

| Sub-Routine |    |   |   |         |

|-------------|----|---|---|---------|

| ML          | OP | В | M | Address |

| Y           |    |   |   | X+1     |

| Y+1         |    |   |   |         |

X - Location of the RETURN JUMP instruction.

X+1 - Location of the instruction following the RETURN JUMP instruction.

Y - Specified location, where number X+l is transmitted.

Y+1 - Location of the next instruction to be executed.

(Example continued on next page)

Step (1) Step (2) Step (3)

Execute X Transmit X+1

Execute Y+1

to low-order 15 bits

of (Y)

Continue with Ysequence of instruction until programmed

otherwise.

#### b. NORMAL JUMP (Set PAK=Y)

Change the program address to obtain the next instruction from the memory location specified by the lower 12 bits of the NORMAL JUMP instruction.

The "b"-modifier may be used.

The third-of-a-word feature may not be used.

The repeat may be used. The repeat sequence is terminated if the Jump occurs, storing the numbers of unperformed repetions in B<sub>7</sub>. If the Jump does not occur, repetition of the instruction continues.

This instruction is used to change series of addresses in a program.

#### Example:

Series A

|    |     | Oer | res v    |         |

|----|-----|-----|----------|---------|

| ML | OP  | В   | M        | Address |

| X  | SLJ |     | 1, 2, 3, |         |

|    |     |     | or Ø     | Y       |

| Series B |    |   |   |         |  |

|----------|----|---|---|---------|--|

| ML       | OP | В | M | Address |  |

| Y        |    |   |   |         |  |

X - Location of Jump instruction

Y - Location of next instruction to be executed

B. Execution Time of Instructions

| <br>Octal  | Mnemonic   | Time in Mi             | croseconds       |

|------------|------------|------------------------|------------------|

| Code       | Code       | Normal                 | Repeat           |

| 0.0        |            |                        | •                |

| 00<br>01   | מואים      | 20                     |                  |

| 02         | ENB        | 40                     |                  |

| 03         | LDB        | 40                     |                  |

| 04         | STB        | 20                     |                  |

| 05         | INB<br>BSK | 32                     |                  |

| 06         | TSK        | 32                     |                  |

|            |            | 20                     |                  |

| 07         | RPT        | 20                     |                  |

| 10         |            |                        |                  |

| 11         | ENA        | 32                     | 12               |

| 12         | LDA        | 40                     | 20               |

| 13         | STA        | 40                     | 20               |

| 14         | COA        | 28                     | 8                |

| 15         | SHA        | Timing depends on an   | nount of shift;  |

| 16         | LSH        | see pages III-28 and I | II-29.           |

| 17         | AJP        | Variable timing depen  | nding on JUMP or |

|            |            | NO JUMP conditions;    | see page III-30. |

| 20         |            |                        |                  |

| 21         | TONIC      | 32                     | 12               |

| 22         | ENQ<br>LDQ | 40                     | 20               |

| 23         | STQ        | 40                     | 20               |

| 24         | COQ        | 36                     | 16               |

| 25         | SHQ        | Timing depends on an   |                  |

| 43         | DIIQ       | see page III-36.       | nount of sitte,  |

| 26         | TAQ        | 32                     | 12               |

| 27         | QJP        | Variable timing deper  |                  |

| 2,         | 201        | NO JUMP conditions;    | _                |

|            |            | TVO DOMESTICATIONS,    | occ page 111-50. |

| 30         |            |                        |                  |

| 31         | ADC        | 32                     | 12               |

| 32         | ADD        | 40                     | 20               |

| 33         | ADR        | 60                     | 40               |

| 34         | RAO        | 60                     | 40               |

| 35         | LAQ        | 48                     | 28               |

| 36         | AQS        | 56                     | 36               |

| 37         | RAQ        | 68                     | 48               |

| <u>-</u> . | A-6        |                        | .= ~             |

| Octal    | Mnemonic | Time in Micros            | econds  |

|----------|----------|---------------------------|---------|

| Code     | Code     | Normal                    | Repeat  |

| 40       |          |                           |         |

| 41       | SBC      | 32                        | 12      |

| 42       | SUB      | 40                        | 20      |

| 43       | SBR      | 60                        | 40      |

| 44       | RSO      | 60                        | 40      |

| 45       | LSQ      | 48                        | 28      |

| 46       | SQS      | 56                        | 36      |

| 47       | RSQ      | 68                        | 48      |

| 50       | LPR      | 44                        | 24      |

| 51       | ALP      | 44                        | 24      |

| 52       | SCO      | 40                        | 20      |

| 53       | SBT      | 44                        | 24      |

| 54       | RLP      | 60                        | 40      |

| 55       | RAL      | 64                        | 44      |

| 56       | RSC      | 60                        | 40      |

| 57       | RSB      | 60                        | 40      |

| 60       | MUL      | Variable timing; see page | III-62. |

| 61       | DIV      | do                        | III-66. |

| 62<br>63 | SCL      | 40                        | 20      |

| 64       | ESK      | 64                        | 44      |

| 65       | USK      | 64                        | 44      |

| 66       | GSK      | 60                        | 40      |

| 67       | LSK      | 60                        | 40      |

| 70       | EXF      | 36                        | 16      |

| 71       | INP      | Variable timing; see page |         |

| 72       | OUT      | do                        | III-78. |

| 73       | TRJ      | do                        | III-80. |

| 74       | SNJ      | do                        | III-81. |

| 75       | SLJ      | do                        | III-83, |

| 76       | SLS      | do                        | III-85. |

| 77       |          |                           | -       |

Note that instructions 00 through 07 are not timed under REPEAT CONTROL.

The method of timing an instruction under REPEAT CONTROL is as follows:

Time of number of timing of normal RPT plus repetitions times instr. plus time of Instr. minus one under RPT instr.

# Example:

Repeat the ENA (11) instruction 15 times:

20 + (14)(12) + 32 = 220 microseconds

#### C. Instruction Code

| Instruction |    | Mnemonic<br>Code | Symbolic Description |

|-------------|----|------------------|----------------------|

| ENTER B     | 01 | (ENB)            | y →B                 |

a. INSTRUCTION DESCRIPTION - Replace the content of the specified B-register with the low-order 15 bits of the instruction.

#### b. SPECIAL FUNCTIONS

- 1. The execution of this instruction causes the repeat sequence to be terminated.

- 2. The B-designator, "b", is used to designate a specific B-box, but the instruction is not modified by the specified B-register before execution.

- The INSTRUCTION MODIFIER, "m", is a part of the constant entering B.

- c. TIMING Normal operation time is 20 microseconds.

- 4. If the B-designator is zero this instruction functions as a "no operation" instruction.

| Instruction | Operation Code | Mnemonic<br>Code | Symbolic Description |

|-------------|----------------|------------------|----------------------|

| LOAD B      | 02             | (LDB)            | $(Y) \rightarrow B$  |

- a. INSTRUCTION DESCRIPTION Add the content of B-box specified to the low-order 15 bits of this instruction, then replace the content of the B-box with the content of the storage location specified by this modified address.

- b. SPECIAL FUNCTIONS (B) is added to m, k and transferred to S before B is loaded from storage. The bits from the storage location may comprise any 8-bit third of a word or the low-order 15 bits of a word.

- Execution of this instruction causes the repeat sequence to be terminated.

- 2. The Bi-designator, "b", is used with this instruction.

- 3. The INSTRUCTION MODIFIER,

"m", as a word-portion designator,

is used with this instruction. If

m = 0, the specified B-register

receives the low-order 15 bits

from the storage location.

- c. TIMING Normal operation time is 40 microseconds.

- 4. If the B-designator is zero, this instruction functions as a "no operation" instruction.

|             | Operation | Mnemonic | Symbolic    |

|-------------|-----------|----------|-------------|

| Instruction | Code      | Code     | Description |

| STORE B     | 03        | (STB)    | (B) → y     |

- a. INSTRUCTION DESCRIPTION Replace the low-order 15 bits of the content of the storage location with the content of the specified B-register.

- b. SPECIAL FUNCTIONS The high-order 9 bits of the storage location will remain unchanged. All arithmetic registers remain unchanged.

- 1. The execution of this instruction causes the repeat sequence to be terminated.

- 2. The B-designator, "b", is used to designate a specific B-box, but the instruction is not modified by the specified B-register before execution. The B-register specified is not changed.

- 3. The INSTRUCTION MODIFIER, "m", has no meaning in this instruction. (Only the low-order 15 bits of the storage location change, regardless of the value of "m".)

- c. TIMING Normal operation time is 40 microseconds.

- 4. If the B-designator is zero, the low-order fifteen bits of the storage location specified will be set to zero.

| Instruction | Operation<br>Code | Mnemonic<br>Code | Symbolic Description |

|-------------|-------------------|------------------|----------------------|

| INCREASE B  | 04                | (INB)            | (B) + y → B          |

- a. INSTRUCTION DESCRIPTION Add the low-order 15 bits of this instruction to the specified B-register.

- b. SPECIAL FUNCTIONS This instruction enables B to advance its address position by any constant.

- Execution of this instruction causes the repeat sequence to be terminated.

- 2. The B-designator, "b", is used to designate a specific B-box, but the instruction is not modified by the B-register before execution.

- The INSTRUCTION MODIFIER, "m", has no meaning in this instruction.

- c. TIMING Normal operation time is 20 microseconds.

- 4. If the B-designator is zero, this instruction functions as a "no operation" instruction.

| Instruction | Operation | Mnemonic | Symbolic                                                          |

|-------------|-----------|----------|-------------------------------------------------------------------|

|             | Code      | Code     | Description                                                       |

| INDEX SKIP  | 05        | (BSK)    | If (B)≥y, skip NI<br>then clear B;<br>If (B)∠y,<br>then (B) +1->B |

a. INSTRUCTION DESCRIPTION - If the content of the specified B-register is greater than or equal to the low-order 15 bits of this instruction, skip the next sequential instruction and clear B. If the content of the specified B-register is less than the low-order 15 bits of this instruction, add one to the specified B-register and execute the next sequential instruction.

#### b. SPECIAL FUNCTIONS

- 1. Execution of this instruction causes the repeat sequence to be terminated.

- 2. The B-designator, "b", is used to designate a specific B-box, but the instruction is not modified by the B-register before execution.

- 3. The INSTRUCTION MODIFIER, "m", has no meaning in this instruction.

- c. TIMING Normal operation time is  $\underline{32}$  microseconds.

- 4. For the purposes of this instruction, numbers which contain a <u>l</u> in the fifteenth bit are regarded as negative.

| Instruction    | Operation | Mnemonic | Symbolic                  |

|----------------|-----------|----------|---------------------------|

|                | Code      | Code     | Description               |

| THRESHOLD SKIP | 06        | (TSK)    | If (B) $\geq_y$ , skip NI |

- a. INSTRUCTION DESCRIPTION If the content of the specified B-register is greater than or equal to the low-order 15 bits of this instruction, skip the next sequential instruction. If the content of the specified B-register is less than the low-order 15 bits of this instruction, continue with the present sequence.

- b. SPECIAL FUNCTIONS This instruction checks the value of (B) without changing its content.

- 1. The execution of this instruction causes the repeat sequence to be terminated.

- 2. The B-designator, "b", is used to designate a specific B-box, but the instruction is not modified by the B-register before execution.

- 3. The INSTRUCTION MODIFIER, "m", has no meaning.

- c. TIMING Normal operation time is 32 microseconds.

- 4. For the purposes of this instruction, numbers which contain a <u>l</u> in the fifteenth bit are regarded as negative.

| Instruction | Operation<br>Code | Mnemonic<br>Code | Symbolic Description |

|-------------|-------------------|------------------|----------------------|

| REPEAT      | 07                | (RPT)            | Execute NI Y times.  |

- a. INSTRUCTION DESCRIPTION Execute the next instruction the number of times indicated by the low-order 12 bits of this instruction, as modified by specified B-box.

- If m = 0, 2, 4, 6 after modification -- No change in the repeated instruction.

- If m = 1 or 3 after modification -- Increase the loworder 15 bits of the repeated instruction by one each time the instruction is executed.

- If m = 5 or 7 after modification -- Decrease the loworder 15 bits of the repeated instruction by one each time the instruction is executed.

- B<sub>7</sub> (bits 00 through 11) is used as the repeat counter.

The repeat is terminated under any one of the following conditions with B<sub>7</sub> containing the count of unperformed repetitions:

- When the instruction being repeated calls for a change of program address, such as jump or skip.

- 2. Upon receipt of an "External Disconnect" signal from external equipment.

- 3. Upon depletion of the repeat count.

- 4. Execution of instructions 01, 02, 03, 04, 05, 06, 07.

- 1. B<sub>7</sub> is decreased by one each time the repeated instruction is executed.

- 2. B-designator, "b", is used.

- 3. The INSTRUCTION MODIFIER, "m", is used with this instruction to specify the address modification of the repeated instruction.

- 4. Since the repeat instruction is an auxiliary instruction, one or more of the registers of the computer may change during the execution of the repeated instruction.

- 5. The repeated instruction is modified by "b" in the initial execution. Thereafter, the "m" of the repeat instruction designates the address modification.

- 6. Repeating an instruction zero times causes that instruction to be skipped.

- c. TIMING Normal operation time is 40 microseconds if Repeat count = 0; if Repeat count = 0, operation

time is 20 microseconds.

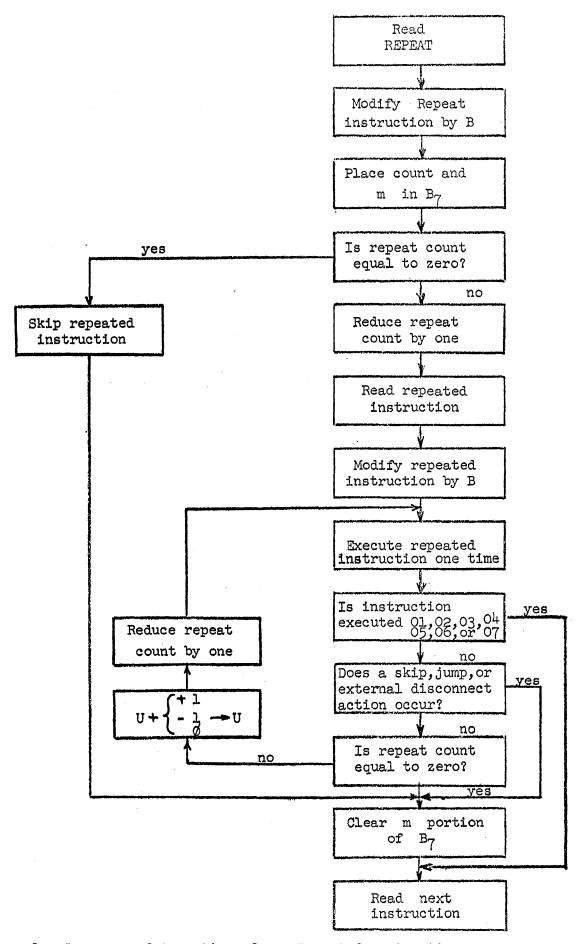

- d. SEQUENCE OF OPERATIONS FOR A REPEATED INSTRUCTION The modifier (specifing the modification of the repeated instruction) is stored in  $B_7$  with the repeat count. Thus, a modification by  $B_7$  includes the modifier. The modifier is cleared from  $B_7$  upon termination of the repeated instruction.

Figure 2 - Sequence of Operations for a Repeated Instruction

| Instruction | Operation<br>Code | Mnemonic<br>Code | Symbolic Description |

|-------------|-------------------|------------------|----------------------|

| ENTER A     | 11                | (ENA)            | Y →A                 |

- a. INSTRUCTION DESCRIPTION Replace the content of the Accumulator with the low-order 15 bits of this instruction as modified by specified B.

- b. SPECIAL FUNCTIONS If "b" is zero, the low-order 15 bits of the instruction enter A as a positive 15-bit number. If "b" is not zero, the low-order 15 bits, plus the content of the designated B-box, enter A as a positive number. In any case the high order 9 bits of A, bits 15 23, will be zero.

- 1. The REPEAT feature is available for use with this instruction.

- 2. The B-designator, "b", is available for use with this instruction.

- 3. The INSTRUCTION MODIFIER, "m", as a modifier, has no meaning in this instruction.

- c. TIMING Normal operation time is 32 microseconds; repeat, 12 microseconds.

| Instruction | Operation<br>Code | Mnemonic<br>Code | Symbolic Description |

|-------------|-------------------|------------------|----------------------|

| LOAD A      | 12                | (LDA)            | (Y) → A              |

a. INSTRUCTION DESCRIPTION - Replace the content of A with the content of the storage location specified by the low-order 15 bits of this instruction as modified by B.

- 1. The REPEAT feature is available for use with this instruction.

- 2. The B-designator, "b", is available for use with this instruction.

- 3. The INSTRUCTION MODIFIER, "m", used as a word-portion designator, is available for use with this instruction.

- c. TIMING Normal operation time is 40 microseconds; repeat operation time, 20 microseconds.

|             | Operation | Mnemonic | Symbolic    |

|-------------|-----------|----------|-------------|

| Instruction | Code      | Code     | Description |

| STORE A     | 13        | (STA)    | (A) → Y     |

- a. INSTRUCTION DESCRIPTION Replace the content of the storage location, specified by the low-order 15 bits of this instruction, as modified by B, with the content of the Accumulator.

- b. SPECIAL FUNCTIONS The Accumulator is unchanged by this operation.

- 1. The REPEAT feature is available for use with this instruction.

- 2. The B-designator, "b", is available for use with this instruction.

- 3. The INSTRUCTION MODIFIER, "m", is used as a word-portion designator in this instruction. Only the portion of the stored information as specified by "m" is altered. Bits 0 to 7 of A may be stored in any designated third of a word.

- c. TIMING Normal operation time is 40 microseconds; repeat, 20 microseconds.

|              | Operation | Mnemonic | Symbolic                  |

|--------------|-----------|----------|---------------------------|

| Instruction  | Code      | Code     | Description               |

| COMPLEMENT A | 14        | (COA)    | $(A^1) \longrightarrow A$ |

- a. INSTRUCTION DESCRIPTION Replace the content of the Accumulator with its one's complement.

- b. SPECIAL FUNCTIONS The instruction may be classified as a "no address" instruction since the low-order 18 bits of the instruction are not used. Complementing of positive zero (all 0's) results in positive, zero.

- 1. The REPEAT feature is available for use with this instruction.

- 2. The B-designator, "b", has no meaning in this instruction.

- The INSTRUCTION MODIFIER, "m", has no meaning in this instruction.

- c. TIMING Normal operation time is 28 microseconds; repeat operation, 8 microseconds.

| Instruction | Operation<br>Code | Mnemonic<br>Code | Symbolic Description              |

|-------------|-------------------|------------------|-----------------------------------|

| SHIFT A     | 15                | (SHA)            | $(A)_{s} \longrightarrow (A)_{f}$ |

- a. INSTRUCTION DESCRIPTION Shift the Accumulator, circularly to the left, the number of bit positions specified by the low-order 6 bits of this instruction as modified by specified B.

- b. SPECIAL FUNCTIONS The maximum shift is 63 bit positions.

- 1. The REPEAT feature is available for use with this instruction.

- 2. The B-designator, 'b', is available for use with this instruction.

- 3. The INSTRUCTION MODIFIER, "m", has no meaning in this instruction.

- c. TIMING Operation time, if 1, 2, 4, 5, 6, 8, 9, or 10 shifts, is 32 microseconds. Operation time if 3, 7, 11, 12, 13, 14, or 15 shifts, is 36 microseconds. Operation time is increased 4 microseconds with each additional four shifts. Operation time for repeat is variable, depending upon number of shifts.

| Instruction | Operation<br>Code | Mnemonic<br>Code | Symbolic Description            |

|-------------|-------------------|------------------|---------------------------------|

| LONG SHIFT  | 16                | (LSH)            | $(AQ)_{g} \rightarrow (AQ)_{f}$ |

- a. INSTRUCTION DESCRIPTION Shift (A) and (Q), as one 48-bit register, circularly to the left the number of bit positions as specified by the low-order 6 bits of this instruction as modified by B.

- b. SPECIAL FUNCTIONS The maximum shift is 63 bit positions.

- 1. The REPEAT feature is available for use with this instruction.

- 2. The B-designator, "b", is available for use with this instruction.

- 3. The INSTRUCTION MODIFIER, "m", has no meaning in this instruction.

- c. TIMING Operation time, if 1, 2, 4, 5, 6, 8, 9, or 10 shifts, is 32 microseconds. Operation time, if 3, 7, 11, 12, 13, 14, or 15 shifts, is 36 microseconds. Operation time is increased by 4 microseconds with each additional four shifts. Operation time for repeat is variable depending upon the number of shifts.

|  |             |      | Mnemonic | •           |

|--|-------------|------|----------|-------------|

|  | Instruction | Code | Code     | Description |

|  | A JUMP      | 17   | (AJP)    |             |

- a. INSTRUCTION DESCRIPTION The Accumulator Jump instruction has eight options, depending on the value of "m" and the present status of the Accumulator.

- If m = 0 and if the content of the Accumulator is zero, do a normal jump; if A is not zero, continue the present sequence.

- If m = 1 and if the content of the Accumulator is not zero, do a normal jump; if the content of the Accumulator is equal to zero, continue the present sequence.

- If m = 2 and if the content of the Accumulator is positive  $(A_{23}=0)$ , do a normal jump; if A is not positive, continue the present sequence.

- If m = 3 and if the content of the Accumulator is negative  $(A_{23}=1)$ , do a normal jump; if A is not negative, continue the present sequence.

- If m = 4 and if the content of the Accumulator is zero do a return jump; if A is not zero, continue the present sequence.

- If m = 5 and if the content of the Accumulator is not zero, do a return jump. If the content of the Accumulator is equal to zero, continue the present sequence.

- If m = 6 and if the content of the Accumulator is positive  $(A_{23}=0)$ , do a return jump; if A is not positive, continue the present sequence.

- If m = 7 and if the content of the Accumulator is negative  $(A_{23}=1)$ , do a return jump; if A is not negative, continue the present sequence.

- b. SPECIAL FUNCTIONS If the trace jump control is on, a return jump to zero sequence will replace either the normal jump or return jump sequence. During this instruction the Accumulator does not change.

- 1. The REPEAT feature is available for use with this instruction, being terminated if the jump condition exists.

- 2. The B-designator, "b", is available for use with this instruction.

- 3. The INSTRUCTION MODIFIER, "m", is used to designate the jump condition.

- c. TIMING For NO JUMP, the normal operation time is 40 microseconds; repeat operation, 20 microseconds. For JUMP, the normal operation time for no trace jump and m = 0,1,2, or 3, is 40-microseconds; for trace jump or m = 4,5,6, or 7, is 56 microseconds.

| Instruction | • | Operation<br>Code | Mnemonic<br>Code | Symbolic Description |

|-------------|---|-------------------|------------------|----------------------|

| ENTER Q     |   | 21                | ((ENQ)           | Y→Q                  |

- a. INSTRUCTION DESCRIPTION Replace the content of the Q-register with the low-order 15 bits of this instruction as modified by B.

- b. SPECIAL FUNCTIONS If "b" is zero, the low-order 15 bits of the instruction enter Q as a positive 15-bit number. If "b" is not zero, the low-order 15 bits, plus the content of the designated B-box, enter Q as a positive number. In any case the high order 9 bits of Q, bits 15 23, will be zero.

- 1. The REPEAT feature is available for use with this instruction.

- 2. The B-designator, "b", is available for use with this instruction.

- 3. The INSTRUCTION MODIFIER, "m", has no meaning in this instruction.

- c. TIMING Normal operation time is 32 microseconds; repeat, 12 microseconds.

|             | Operation | Mnemonic | •           |

|-------------|-----------|----------|-------------|

| Instruction | Code      | Code     | Description |

| LOAD Q      | 22        | (LDQ)    | (Y) → Q     |

a. INSTRUCTION DESCRIPTION - replace the content of the Q-register with the content of the storage location specified by the low-order 15 bits of this instruction, as modified by B.

- 1. The REPEAT feature is available for use with this instruction.

- 2. The B-designator, 'b', is available for use with the instruction.

- 3. The INSTRUCTION MODIFIER, "m", is used as a word-portion designator with this instruction.

- c. TIMING Normal operation time is 40 microseconds; repeat, 20 microseconds.

| Instruction | Operation | Mnemonic | Symbolic                |

|-------------|-----------|----------|-------------------------|

|             | Code      | Code     | Description             |

| STORE Q     | 23        | (STQ)    | $(Q) \longrightarrow Y$ |

- a. INSTRUCTION DESCRIPTION Replace the content of the storage location, specified by the low-order 15 bits of this instruction as modified by B, with the content of the Q-register.

- b. SPECIAL FUNCTIONS The Q-register remains unchanged by this operation.

- 1. The REPEAT feature is available for use with this instruction.

- 2. The B-designator, 'b', is available for use with this instruction.

- 3. The INSTRUCTION MODIFIER, "m", is used as a word-portion designator with this instruction. Only the portion of the stored information as specified by "m" is altered. Bits 0 to 7 of Q may be stored in any designated third of a word.

- c. TIMING Normal operating time is 40 microseconds; repeat, 20 microseconds.

| Instruction  | Operation<br>Code | Mnemonic<br>Code | Symbolic Description    |

|--------------|-------------------|------------------|-------------------------|

| COMPLEMENT Q | . 24              | (COQ)            | $(Q^{1}) \rightarrow Q$ |

- a. INSTRUCTION DESCRIPTION Replace the content of the Q-register with its one's complement.

- b. SPECIAL FEATURES The instruction is a "no-address" instruction since the low-order 18 bits of the instruction are not used. Complementing of positive zero (all 0's) results in a negative zero (all 1's).

- 1. The REPEAT feature is available for use with this instruction.

- 2. The B-designator, "b", has no meaning in this instruction.

- 3. The INSTRUCTION MODIFIER, "m", has no meaning in this instruction.

- c. TIMING Normal operating time is 36 microseconds; repeat, 16 microseconds.

|             | Operation | Mnemonic | Symbolic                    |

|-------------|-----------|----------|-----------------------------|

| Instruction | Code      | Code     | Description                 |

| SHIFT Q     | 25        | (SHQ)    | $(Q)_{g} \rightarrow Q_{f}$ |

| 01111 1 %   |           | (511,2)  | \~/s ~ f                    |

- a. INSTRUCTION DESCRIPTION Shift Q circularly to the left the number of bit positions specified by the low-order 6 bits of this instruction as modified by B.

- b. SPECIAL FUNCTIONS The maximum shift is 63 bit positions.

- 1. The REPEAT feature is available for use with this instruction.

- 2. The B-designator, "b", is available for use with this instruction.

- 3. The INSTRUCTION MODIFIER, "m", has no meaning in this instruction.

- c. TIMING Operating time for 1, 2, 4, 5, 6, 8, 9, or 10 shifts is 32 microseconds. Operation time, if 3, 7, 11, 12, 13, 14, or 15 shifts, is 36 microseconds. Operation time is increased 4 microseconds with each additional four shifts.

| Instructi |   |    |   | Operation<br>Code | Mnemonic<br>Code | Symbolic Description |

|-----------|---|----|---|-------------------|------------------|----------------------|

| TRANSFER  | A | TO | Q | 26                | (TAQ)            | (A) → Q              |

- a. INSTRUCTION DESCRIPTION Replace the content of the Q-register with the content of the Accumulator.

- b. SPECIAL FUNCTIONS This instruction is a "no-address" instruction, since the low-order 18 bits are not used. The A-register remains unchanged and the Q-register is equal to the Accumulator after executing the instruction.

- 1. The REPEAT feature has no meaning in this instruction.

- 2. The B-designator, "b", has no meaning in this instruction.

- 3. The INSTRUCTION MODIFIER, "m", has no meaning in this instruction.

- c. TIMING Normal operating time is 32 microseconds; repeat, 12 microseconds.

| Instruction | Operation<br>Code | Mnemonic<br>Code | Symbolic Description |

|-------------|-------------------|------------------|----------------------|

| Q JUMP      | 27                | (QJP)            |                      |

- a. INSTRUCTION DESCRIPTION This instruction has eight options, depending upon the value of "m" and the present status of the Q-register.

- If m = 0 and if Q is positive ( $Q_{23}=0$ ), do a normal jump; if Q is not positive, continue the present sequence. Then in either case, shift Q circularly left one bit position.