Remington Rand

NNSHAHA

1902

ENGINEERING RESEARCH ASSOCIATES DIVISION

A 9 E

ST PA

PX 71871

SECTION 4. THEORY OF OPERATION

VOLUME TWO

(TYPE 2300C1)

THE ERA 1103 COMPUTER SYSTEM

PX 71871

# TABLE OF CONTENES VOLUME 2

# SECTION 4 THEORY OF OPERATION

| Paragraph | Title                                                                                                                                                                                                                                                                                                | Page                                         |  |  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|--|--|

| 1.        | General                                                                                                                                                                                                                                                                                              | 4-1                                          |  |  |  |  |  |  |

| 2.        | Glossary of Abbreviations and Terms                                                                                                                                                                                                                                                                  |                                              |  |  |  |  |  |  |

| 3.        | Block Diagrams                                                                                                                                                                                                                                                                                       |                                              |  |  |  |  |  |  |

| 4.        | Unit Signal Diagrams and Unit<br>Chassis Schematic Diagrams                                                                                                                                                                                                                                          | 4-5                                          |  |  |  |  |  |  |

| 5.        | Diagram Symbols                                                                                                                                                                                                                                                                                      | 4-7                                          |  |  |  |  |  |  |

|           | <ul> <li>a. General</li> <li>b. Tube Element Connections</li> <li>c. Shorthand Schematic Symbols</li> <li>d. Block Symbols</li> </ul>                                                                                                                                                                | 4-7<br>4-7                                   |  |  |  |  |  |  |

| 6.        | Storage Section                                                                                                                                                                                                                                                                                      | 4-21                                         |  |  |  |  |  |  |

|           | <ul> <li>a. General</li> <li>b. Storage Address Register</li> <li>c. Storage Class Translator</li> <li>d. Storage Class Control</li> <li>e. Magnetic Drum Storage System</li> <li>f. Magnetic Core Storage System</li> <li>g. Storage in Q and A</li> <li>h. Magnetic Tape Storage System</li> </ul> | 4-21<br>4-24<br>4-25<br>4-27<br>4-33<br>4-54 |  |  |  |  |  |  |

| 7.        | Arithmetic Section                                                                                                                                                                                                                                                                                   | 4-70<br>4-70<br>4-72                         |  |  |  |  |  |  |

|           | <ul> <li>d. Accumulator</li> <li>e. Shift Control Circuitry (SK, SKT, and SKC)</li> <li>f. Arithmetic Sequence Control</li> </ul>                                                                                                                                                                    | 4-79                                         |  |  |  |  |  |  |

| 8.        | Input and Output Section                                                                                                                                                                                                                                                                             |                                              |  |  |  |  |  |  |

|           | a. Generalb. Typewriter Systemc. High-Speed Punch Systemd. 10B-10A System                                                                                                                                                                                                                            | 4-105<br>4-109<br>4-110                      |  |  |  |  |  |  |

|           | e. Photoelectric Tape Reader System                                                                                                                                                                                                                                                                  | 4-113                                        |  |  |  |  |  |  |

Ę

Remington Rand

ENGINEERING RESEARCH ASSOCIATES DAVISAGE

| Paragraph |        | <u>Title</u> '                           |   |     | Page  |

|-----------|--------|------------------------------------------|---|-----|-------|

| 9.        | Contro | )] Section                               |   |     | 4-122 |

|           | a.     | General                                  | • |     | 4-122 |

|           | b.     | Master Clock System (CSS, CRC, PDC)      |   |     | 4-122 |

|           | C.     | Main Pulse Distributor                   | • | • • | 4-128 |

|           | d.     | Program Control Register (MCR, UAK, VAK) |   |     |       |

|           | e.     | Main Control Translator                  |   |     |       |

|           | f.     | Command Timing Circuits                  |   |     |       |

|           | g.     | Program Address Counter                  |   |     |       |

|           | h.     | Repeat Sequence Control                  |   |     |       |

|           | i.     | Fault Detector                           |   |     |       |

|           | 1.     | Stop Control                             |   |     |       |

|           | k.     | Manual and Relay Controls                |   |     |       |

| 10.       | Power  | Supply and Distribution                  |   | • • | 4-103 |

|           | а.     | General                                  | • |     | 4-173 |

|           | b.     | Main Power Supply                        |   |     | 4-103 |

|           | C,     | Magnetic Core Storage (MC) Power Supply  | • | • • | 4-158 |

| 11.       | Cooli  | ng System                                |   | • • | 4-183 |

|           | a.     | Cooling Air                              |   |     | 4-183 |

|           | b,     | Cooling Water                            |   |     |       |

| 12.       | Prote  | ctive Interlocks                         | • |     | 4-184 |

|           | ð,     | General                                  |   |     | 4-184 |

|           | b.     | Fault Interlocks                         |   |     |       |

|           | с,     | Emergency Interlocks                     |   |     |       |

# APPENDIX B TIMING SEQUENCES

| Paragraph | Title                       | Page |

|-----------|-----------------------------|------|

| 1         | General                     | 8-1  |

| 2.        | Command Timing Sequences    | B-1  |

| 3.        | Subcommand Timing Sequences | E2   |

| 4.        | Location of Tables          | B-4  |

Remington Rand

ENGINEERING RESEARCH ASSOCIATES OWNER

11

# LIST OF FIGURES VOLUME 2

## SECTION 4 THEORY OF OPERATION

Title

| 4-1  | Tube Element Connections                          |

|------|---------------------------------------------------|

| 4-2  | Standard Flip-flop Stage                          |

| 4-3  | Standard Cathode Follower                         |

| 4-4  | Standard Inverter Stage                           |

| 4-5  | Standard Gate Stage                               |

| 4-6  | Standard Amplifier Stage                          |

| 4-7  | Standard Pulse Transformer Stages                 |

| 4-8  | Portion of Typical Schematic-type Diagram         |

| 4-9  | Block Symbols                                     |

| 4-10 | Block Diagram Representation of (Figure 4-8) 4-20 |

| 4-11 | MD Locating Circuits                              |

| 4-12 | Typical Magnetic Core and Central Wires           |

| 4-13 | Writing a "O" When the Core was in "O" State 4-41 |

| 4-14 | Writing a "1" When the Core was in "0" State      |

| 4-15 | Writing a "O" When the Core was in "1" State      |

| 4-16 | Writing a "1" When the Core was in "1" State      |

| 4-17 | Reading a Core in the "O" State                   |

| 4-18 | Reading a Core in the "1" State                   |

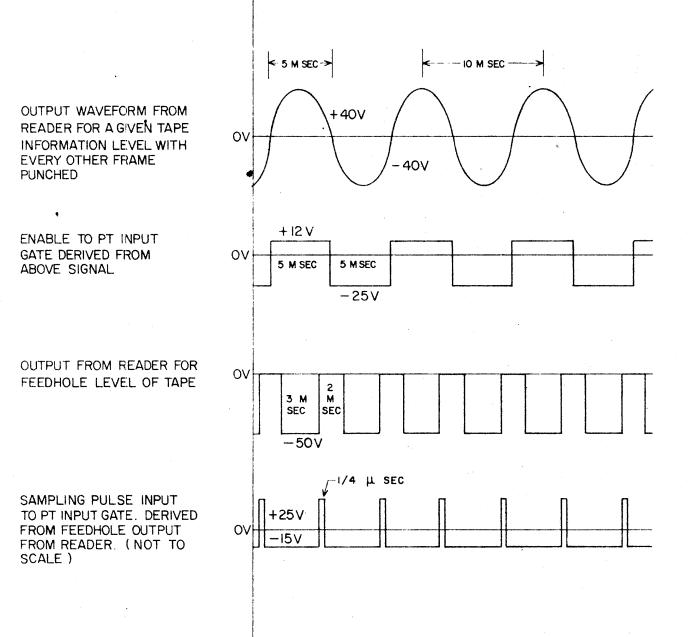

| 4-19 | Voltage Wave Forms from Ferranti Reader           |

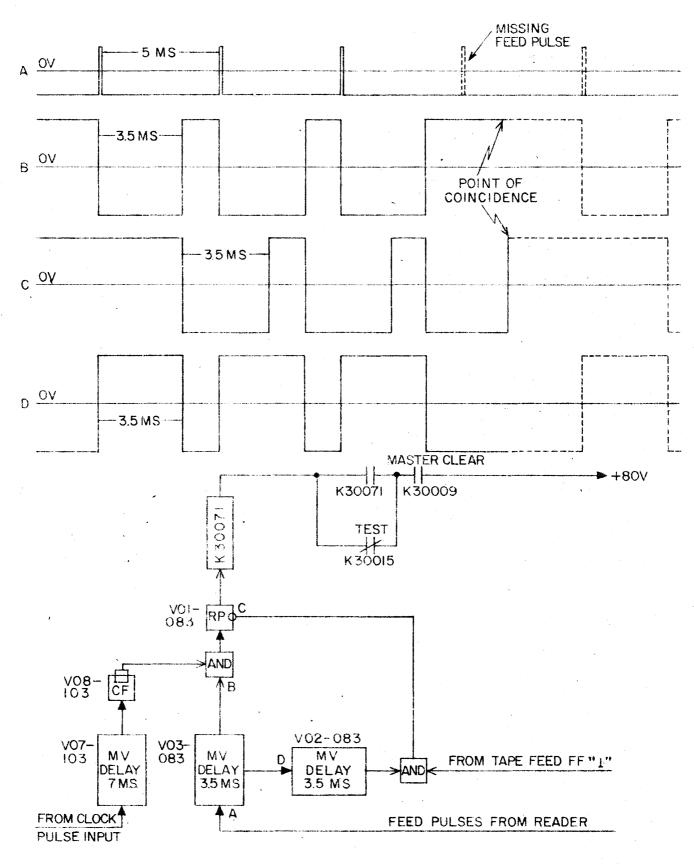

| 4-20 | Missing Feed Pulse Circuit and Wave Form          |

## LIST OF TABLES

#### Table Number Title 4-1 Principal Characteristics of each Storage Class . . . . 4-22 4 - 24-3 4-4 4-5 Portions of CTC $\ldots$ 4-134 4-6 4-7 4 - 8Normal ON-OFF Sequence of Operations for Main . Equipment Power Supply 4-9 Sequence of Operations for Various Voltage Failures 4-10 Normal ON-OFF Sequence of Operation for Magnetic 4-11 4-12 Sequence of Operations for Various Voltage Failures or Emergency Circuits Interruptions in MC Power Supply, 4-181

Figure Number

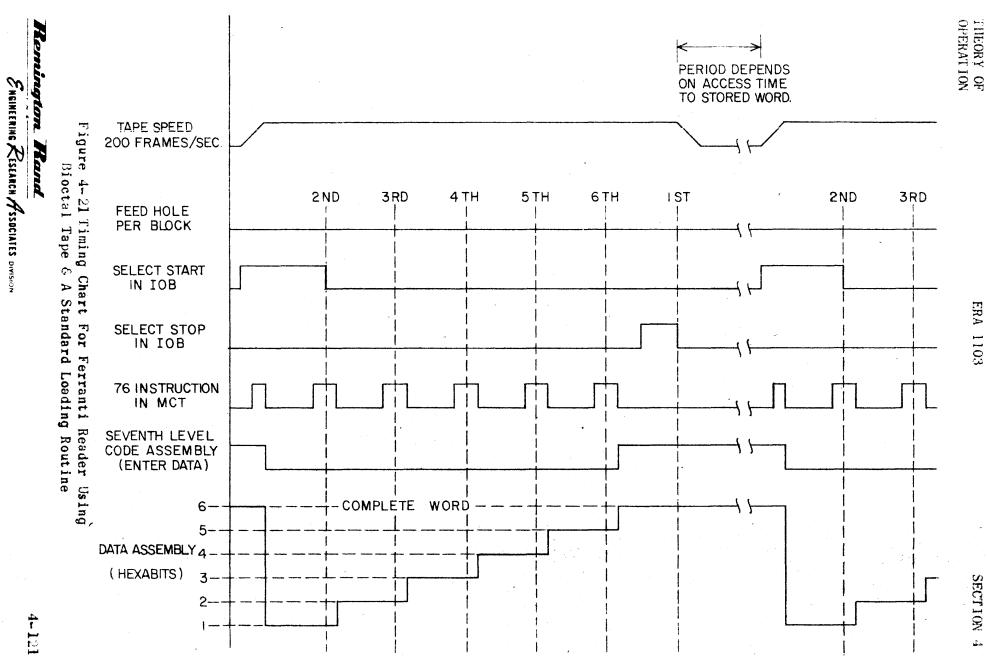

4-21

iii

# Page . 4-8

Page

#### SECTION 4

### THEORY OF OPERATION

#### 1. GENERAL

This section discusses the logical operation of the various sections of the ERA 1103 Computer System and those systems which serve as adjuncts to the logical circuitry such as power supplies, power distribution, protective interlocks, and the air cooling system. The emphasis of explanations is placed on "what" each circuit does logically rather than "how" each circuit operates electrically in the accomplishment of its function. This approach is taken because of the relatively simple electronic principles involved. The system, generally, is built of a great number of similar circuits and stages which are adequately explained in the early paragraphs of this section; thus, a general treatment of computer circuits is given which applies to most of the systems within the equipment. Where unique circuits are encountered, their operation is described at the point of use rather than in the general theory paragraphs.

The system is composed of four major logical sections: the Storage Section, the Arithmetic Section, the Input and Output Section, and the Control Section. Each of these sections is further divided into logical systems which are the subjects of the principal subparagraphs. Each portion of the system is covered by block diagrams beginning with a system block diagram and then going to block diagrams of the system. The block diagrams show only the "decision elements" of the circuits; the strictly signal manipulating stages, such as amplifiers, inverters, pulse transformer, etc., are omitted so that the functions of the circuits are clearly defined. The electronic diagrams which include all components are of two types: the "schematic diagrams" which are basic electrical drawings of physical entities such as chassis and rack units, and the "unit signal diagrams" which are schematic diagrams to which signal names and source and destination information have been added. A schematic diagram is included of each "chassis type", whereas a unit signal diagram is included for each "chassis position" in the system.

The information presented in this section covers only the computer proper and several of its standard input and output devices. Information on optional peripheral equipment can be found in appropriately titled volumes supplied with such devices and includes sufficient information to explain their operation as part of the system.

# 2. GLOSSARY OF ABEREVIATIONS AND TERMS

The 72-bit Accumulator  $(A_{71}, A_{70}, \ldots, A_0)$

The left-hand (most significant) 36 bits of A

AL.

A

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

- A<sub>R</sub> The right-hand (least significant) 36 bits of A

- ATK The Angular Index Counter

- $\rightarrow$  (Arrow) Transmit, such as  $A_R \rightarrow X$

- AR A ten-stage Address Register, used to store a Magnetic Core address during a reading or writing operation.

- ARAC The Arithmetic Register Access Control

- ASC The Arithmetic Sequence Control

- Bit Binary digit

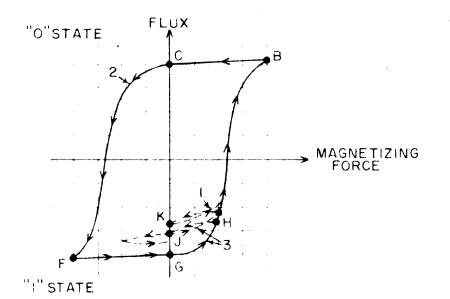

- Core A small toroid of Ferrite capable of storing a binary digit (bit) equal to "1" or "0", depending upon the direction of remnant magnetization of the toroid.

- CRC The Clock Rate Control

- CSS The Clock Source Selector

- CTC The Command Timing Circuits

- D(Q) A 72-bit word whose right-hand 36 bits are the content of Q and whose left-hand 36 bits are all alike and equal to the left-most bit of the content of Q.

- D(u) A 72-bit word whose right-hand 36 bits are the contents of u and whose left-hand 36 bits are all alike and equal to the left-most bit of the content of u.

- $F_1$  A Fixed Address 00000 (or 40001 depending on a switch setting)

- F<sub>2</sub> A Fixed Address 00001

- HPC The High-Speed Punch Control

- HPR The High-Speed Punch Register

- I/D Inhibit/Disturb, a term used to describe circuits which control the selective writing of information in cores.

- IR Magnetic Core Input Register, a 36-stage register that serves as a transfer register between X and the cores.

- j A one-digit octal number  $(u_{14}, u_{13}, u_{12})$

- k The Shift Count  $(v_6, v_5, \ldots, v_0)$

Engineering Research Associates Division

- L(Q)(u) A 72-bit word whose left-hand 36 bits are zeros and each of whose right-hand 36 bits is given by the bit-by-bit product of the corresponding bits of Q and u.

- L(Q)'(v) A 72-bit word whose left-hand 36 bits are zeros and each of whose right-hand 36 bits is given by the bit-by-bit product of the corresponding bits of v and the complement of Q.

- Matrix A printed-circuit frame containing 1024 magnetic cores held in a 32 x 32 array by wires threaded through the cores.

- MC A prefix denoting "Magnetic Core", used to designate signals belonging to the Magnetic Core Storage System.

- MCAC Magnetic Core Access Control. A flip-flop control circuit that produces sequences for execution of reading and writing operations in the Magnetic Core Storage System.

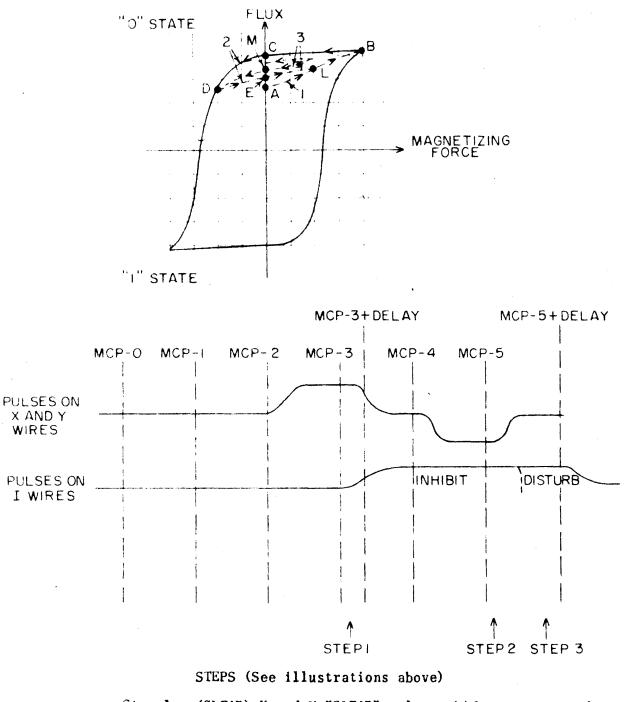

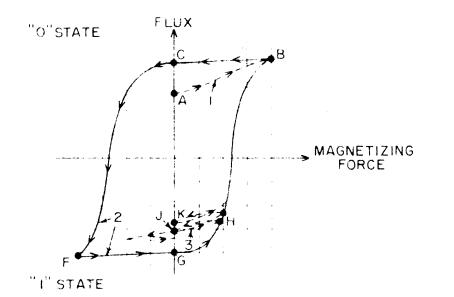

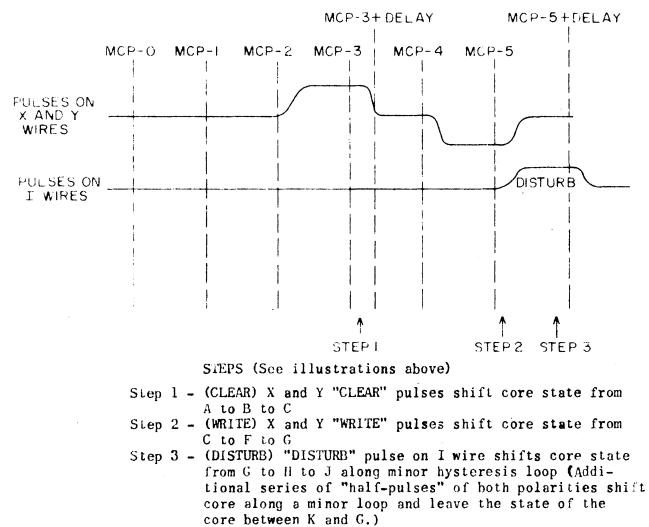

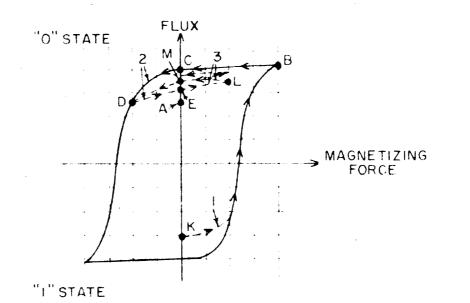

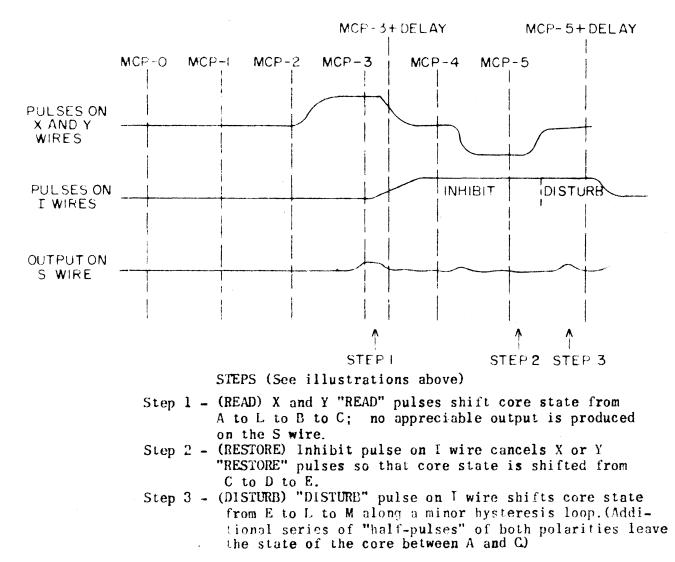

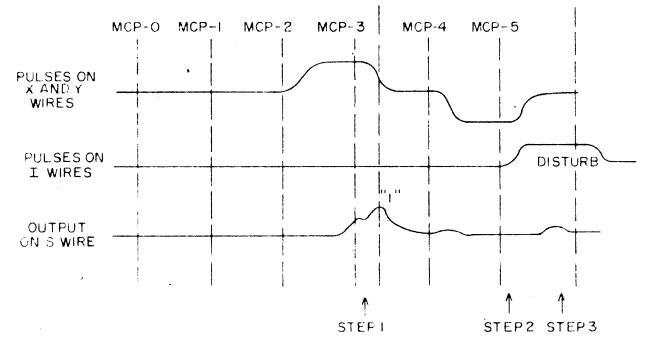

- MCP Magnetic Core Pulse, usually followed by a number, such as MCP-1, MCP-2, etc. Basic timing pulse used in the Magnetic Core Access Control.

- MCPD Magnetic Core Pulse Distributor, a three-stage binary counter and distributor that distributes a sequence of five MCP's.

- MCR The Main Control Register, a part of PCR.

- MCS An abbreviation for the Magnetic Core Storage System. This abbreviation followed by a subscript number denotes a particular stage (digit) of MCS. For example: MCS<sub>0</sub> represents the digit which stores the lowest-order bits (2<sup>0</sup>), and MCS<sub>35</sub> represents the digit which stores the highest-order bits (2<sup>35</sup>).

- MCT The Main Control Translator

- MD The Magnetic Drum Storage System

- MDAC The Magnetic Drum Storage Access Control

- MP A MAIN PULSE, usually followed by a numeral

- MPD The Main Pulse Distributor

- MT The Magnetic Tape Storage System

- MTI The Magnetic Tape Storage Input Register

- MTO The Magnetic Tape Storage Output Register

- MTSC The Magnetic Tape Storage Sequence Control

- A four-digit octal number  $(u_{11}, u_{10}, \ldots, u_0)$

Remington Rand

n

ENGINEERING RESEARCH ASSOCIATES DIVISION

| PAK    | The Program Address Counter                                                                              |

|--------|----------------------------------------------------------------------------------------------------------|

| ()     | (Parentheses) Denotes "the content of"                                                                   |

| PCR    | The Program Control Registers, MCR, UAK, and VAK                                                         |

| PDC    | The Pulse Distributor Control                                                                            |

| ·      | (Prime) Denotes "the complement of" such as Q', X', etc.                                                 |

| Q      | The 36-bit Q-Register (Q35, Q34,, Q0)                                                                    |

| RSC    | The Repeat Sequence Control                                                                              |

| S ( u) | A 72-bit word whose right-hand 36 bits are the content of w<br>and whose left-hand 36 bits are all zeros |

| SAR    | The Storage Address Register                                                                             |

| SCC    | The Storage Class Control                                                                                |

| SCT    | The Storage Class Translator                                                                             |

| SK     | The Shift Counter (SAR <sub>6</sub> , SAR <sub>5</sub> ,, SAR <sub>0</sub> )                             |

| SKC    | The Shift Counter Control                                                                                |

| TWC    | The Typewriter Control                                                                                   |

| TWR    | The Typewriter Register                                                                                  |

| ų      | The first execution address $(i_{29}, i_{28}, \dots, i_{15})$                                            |

| UAK    | The U-Address Counter, a part of PCR                                                                     |

| v      | The second execution address ( $i_{14}$ , $i_{13}$ ,, $i_0$ )                                            |

| VAK    | The V-Address Counter, a part of PCR                                                                     |

| W      | The v-address portion of a Repeat instruction                                                            |

| x      | The X-Register (X <sub>35</sub> , X <sub>34</sub> ,, X <sub>0</sub> )                                    |

| У      | The address of the current instruction                                                                   |

|        |                                                                                                          |

3. BLOCK DIAGRAMS

IT917 Xq

Two types of block diagrams are included in this instruction book. The Block Diagram, ERA 1103 Computer System, in Envelope #1 of Volume 7 is a "higher level" type of block diagram composed of block symbols which represent each

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION principle circuit of the computer. The other block diagrams are of the "stage level" type, each composed of block symbols which represent the logical circuits or stages of a particular system of the computer.

The purpose of the Block Diagram, ERA Computer System, is to show each principle circuit of the computer and its relation to the other circuits. On this diagram, the principle sections of the computer are shown as follows: the Storage Section consisting of the Magnetic Drum, Magnetic Core, and Magnetic Tape Storage System is in the top half of the diagram; the Control Section is in the lower left corner; the Arithmetic Section consisting of principle multipurpose registers (X, Q, and A) and various control circuits is in the lower center portion of the drawing; and the Input and Output Section consisting of IOA, IOB, the Photoelectric Tape Reader, the Typewriter System, and the High-Speed Punch System is in the lower right-hand corner.

The purpose of the other block diagrams is to show the operations occurring in each of the principle circuits of the computer system. In these diagrams. each stage or subcircuit that performs a function is assigned a symbol called a "block symbol". If a stage does not perform a function, it is omitted. For example, such stages or subcircuits as inverters, pulse transformer, DC restorers, etc. which merely perform signal manipulation and have no logical purpose are not included in block diagrams. Similarly, if an amplifier is used only to amplify a signal, it is not shown on a block diagram; however, where an amplifier's screen grid bias level is controlled to permit that stage to serve as a gate as well as an amplifier, then the amplifier is represented since it performs a logical operations. It should be emphasized that logical elements on the Block Diagrams (particularly, AND, OR and NOT circuits) are represented on the basis of "what" they do. An analysis of their circuitry on a schematic-type drawing is essential in many cases to an understanding of actually "how" they operate. One or more block diagrams of this type have been made for each system of the computer, depending upon the complexity of the system.

"Stage level" block diagrams are the basic references for this entire section. As the text for each system is read, the system's block diagram (Volume 7) should be at hand and should be studied in conjunction with the text. After each of the principle sections of the computer is studied, the section should be located on the Block Diagram, ERA 1103 Computer System, so that the overall function of the section can be reviewed in relation to the other sections of the computer.

## 4. UNIT SIGNAL DIAGRAMS AND UNIT CHASSIS SCHEMATIC DIAGRAMS

The ERA 1103 computer is constructed out of a large number of unit chassis of the 74-pin plug-in type and of the 19-inch relay rack mounting type. Although over 400 unit chassis are used, there are only about 85 distinct types of units. This is because one chassis type may be used more than once where circuit similarities exist. In those cases where there are more than one of the same type used, the unit chassis are interchangeable as to their place in the equipment; i.e. chassis of the same type (same unit chassis construction) may be used for various similar functions.

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

To show how these chassis are interconnected, unit signal diagrams are provided. Essentially a unit signal diagram is the schematic diagram of a unit chassis associated with a particular physical location within the equipment. Thus where two or more identically constructed unit chassis are employed for different applications (as for different stages of a register), their unit signal diagrams will be exactly the same schematically, but will differ in regard to signal designation, inputs and outputs utilized, and origin and destination of signals. Thus, unit signal diagrams are used as circuit diagrams. Each is a schematic of a particular unit chassis, and it shows how that chassis is associated with the rest of the equipment. It is marked to show the sources and destinations of all voltages and signals employed in the chassis. A set of unit signal diagrams is provided for each major section of the equipment. These diagrams are in Volumes 8 through 14, grouped as shown in Table 4-1 below.

## TABLE 4-1

LIST OF UNIT SIGNAL DIAGRAMS

| Volume | Unit Signal Diagram Sets                | Symbol Series  |  |

|--------|-----------------------------------------|----------------|--|

| 8      | Operator's Table                        |                |  |

|        | Relay Panel                             | 26100          |  |

|        | Photoelectric Tape Reader Power         | 94900          |  |

|        | Supply<br>Web Speed Durch               | 26200<br>26300 |  |

|        | High Speed Punch                        | 26400          |  |

|        | Typewriter<br>Whataalaatrig Tapa Deador |                |  |

|        | Photoelectric Tape Reader               | 26700          |  |

|        | Supervisory Control Cabinet             |                |  |

|        | Supervisory Control Panel               | 40000          |  |

|        | Address Monitor                         | 41000          |  |

|        | Address monitor                         | 41000          |  |

| 9      | Arithmetic Cabinet                      | 10000          |  |

| 10     | Control Cabinet                         | 30000          |  |

| 11     | Magnetic Core Storage Cabinet           |                |  |

|        | Magnetic Core Storage System            | 55000          |  |

|        | Magnetic Core Storage Power Sup         |                |  |

|        |                                         | pi) 00000      |  |

| 12     | Magnetic Drum Storage Cabinet           | 60000          |  |

|        |                                         | 00000          |  |

| 13     | Magnetic Tape Storage Cabinet           | 70000          |  |

|        |                                         |                |  |

| 14     | Main Power Supply                       | 80000          |  |

|        |                                         |                |  |

|        | Motor-Generator Assembly                | 88000          |  |

|        |                                         |                |  |

|        | Blower Cabinet                          | 90000          |  |

Remineston Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

In the Arithmetic Cabinet, Control Cabinet, Magnetic Core Storage System, Magnetic Drum Storage Cabinet, and Magnetic Tape Storage Cabinet sets, the drawings are arranged consecutively by the symbol series numbers of the 74-pin jacks which mount the chassis. In all other sets, the drawings are arranged consecutively by unit symbol series number or by physical location in the cabinet.

The unit schematic diagrams are found in Volume 15. These are to be used in conjunction with the test procedures explained in the separate ERA 1103 Test Equipment Manual, supplied with the ERA 1103 Test Equipment.

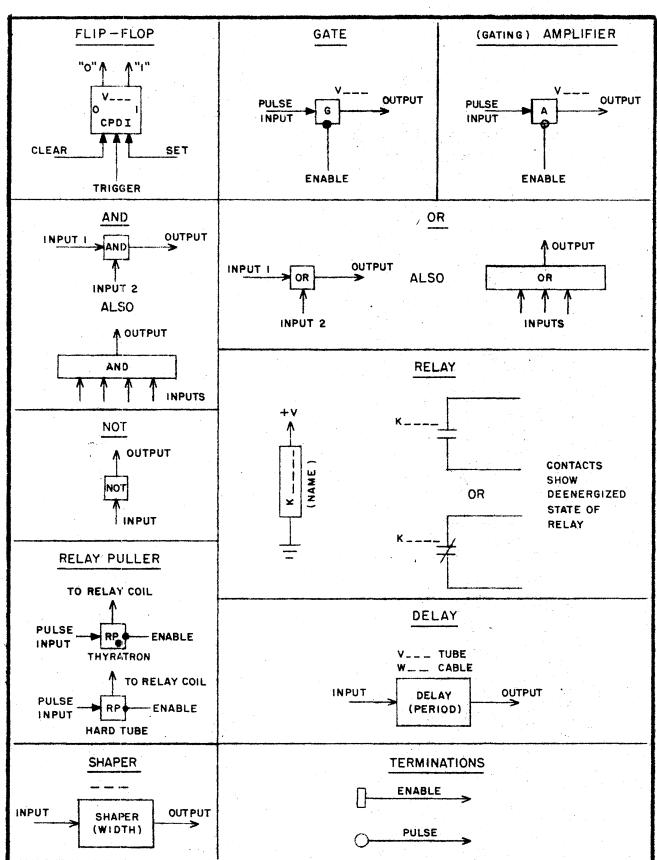

#### 5. DIAGRAM SYMBOLS

a. GENERAL - To conserve space on each of the three kinds of diagrams, block-type symbols are used where possible. Unit signal diagrams and unit chassis schematic diagrams employ special "shorthand symbols" to represent six "standard" circuits, which are used a great number of times throughout the computer. Block diagrams, on the other hand, are composed entirely of block symbols. The symbols used on the block diagrams are different from those used on schematic diagrams. Each symbol by its size, shape, inputs, outputs, and other identifying information represents a particular circuit or a particular logical element. The following subparagraphs explain the basis on which the symbols were chosen, illustrate the various symbols for each type of diagram, and explain what each symbol represents.

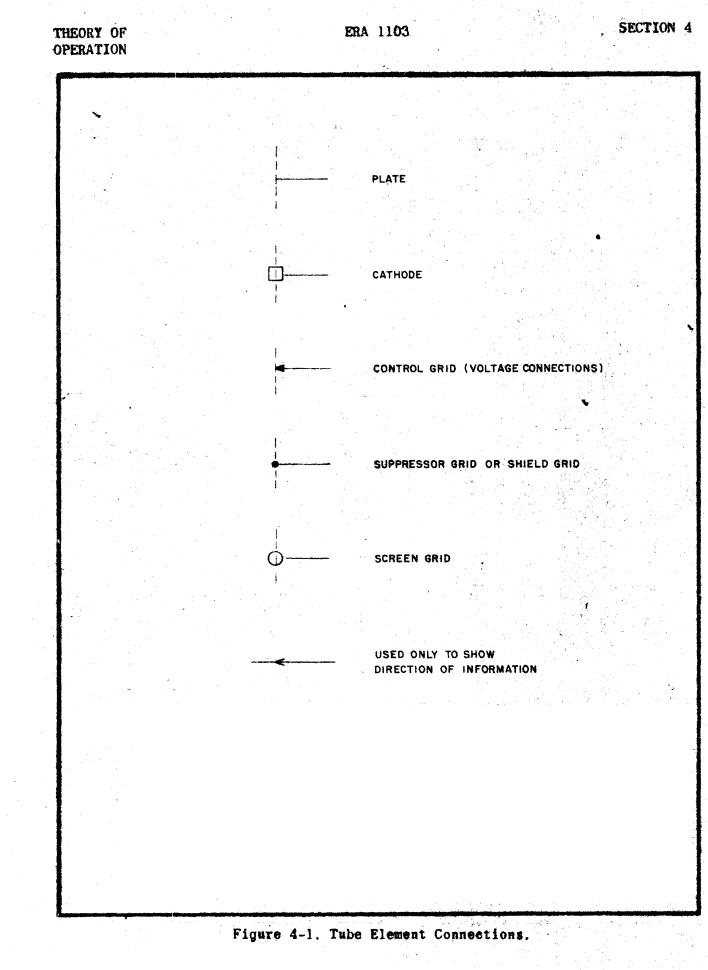

b. TUBE ELEMENT CONNECTIONS. - Symbols for the various tube element connections are shown in Figure 4-1. These symbols are used on all three types of diagrams and should be memorized by maintenance personnel.

c. SHORTHAND SCHEMATIC SYMBOLS. - The specific symbols used on schematic and unit signal diagrams are discussed in the following subparagraphs. If a stage or subcircuit is used repeatedly throughout the equipment and is identical wherever it appears, it is called a "standard stage." All standard stages of the same type are identical electrically; e.g., two standard stage flip-flops receiving identical input signals will, theoretically, produce identical outputs. Each of the principal standard stages explained below in detail will always be found represented by its respective "shorthand schematic symbol" when it appears on a schematic-type diagram.

The principal standard stages are flip-flops, cathode followers, inverters, gates, amplifiers, and pulse transformers,

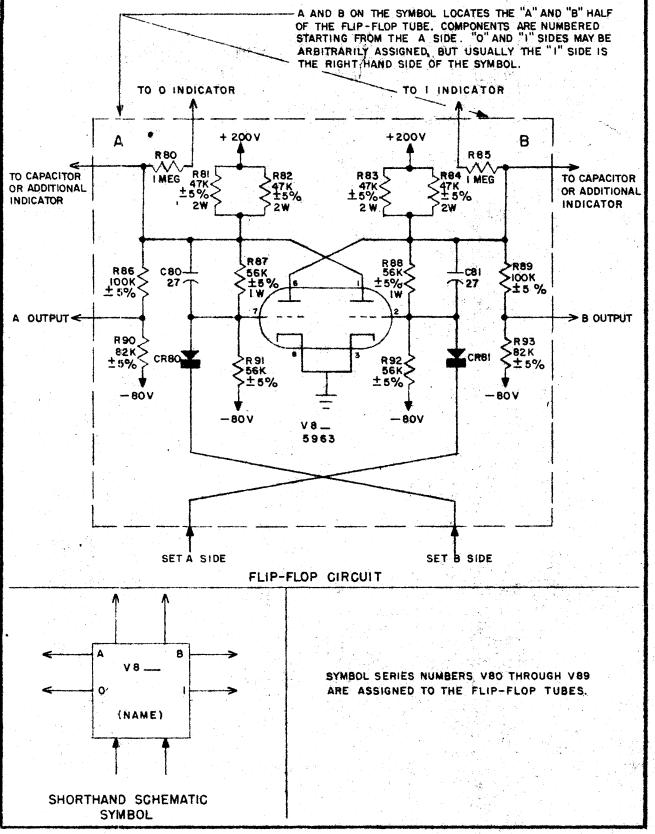

1. FLIP-FLOP - The Eccles-Jordan trigger circuit, or flip-flop, is a form of multivibrator employing direct coupling between the plates and grids of two tubes. The standard flip-flop stage circuit employed in this equipment utilizes a 5963 twin triode tube. A flip-flop circuit is not a free-running multivibrator; rather it is a circuit possessing two stable conditions of equilibrium. For example, in Figure 4-2 below, one condition of equilibrium exists if the triode in side "A" of the flip-flop tube is conducting and the triode in side "B" is cut off, and the other condition of equilibrium exists if the triode in side "A" is cut off and side "B" is conducting. Regardless of which of these two states the flip-flop is in, it will remain in the current state until some external impulse causes it to reverse its state. After such a reversal, the flip-flop will remain in the second state until another external

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

**Remington. Rand.** ENGINEERING RESEARCH ASSOCIATES DIVISION

PX 71871

# Figure 4-2. STANDARD flip-flop Stage.

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

impulse is applied to revert the flip-flop to its first state. The term "flipflop" is derived from this property of "flopping" from state to state.

Since the circuitry in both halves of the flip-flop is identical, it would seem that equal plate current should flow through the triode in each half when plate voltage is applied; however, slight unbalances will always be present. This unbalance will cause a greater plate current to flow in one of the tube's twin triodes when plate voltage as applied. If the greater plate current flows in the triode in side "A", a proportionally larger voltage drop will occur across plate resistors R83 and R84 in side "B"; therefore, the voltage at the plate of the triode in side "A" will be lower than that at the plate of the triode in side "B". The lower plate potential at the triode in side "A" will be applied to the grid of the triode in side "b" through the voltage divider consisting of R88 and R92. The decreasing potential at this grid will cause a further decrease in the plate current of the triode in side "b". The decrease of current in side "B" will cause a corresponding rise in its plate voltage. This rise in plate voltage will be applied to the grid of the triode in side "A" through the voltage divider consisting of R87 and R91. These incremental changes will continue until a state of equilibrium is reached, at which time the triode in side "B" will be cut off and the triode in side "A" will be fully conducting.

To reverse the state of equilibrium, a negative-going pulse is applied through CR80 to the grid of the triode in side "A". The increase in bias on the grid of this triode causes a drop in its plate current. The drop in plate current causes a rise in plate voltage, which is applied to the grid of the triode in side "E" through the voltage divider consisting of R88 and R92; therefore, the rise in plate voltage causes the triode in side "E" to start to conduct. This triode, when conducting, has a low plate voltage which is applied to the grid of the triode in side "A" through the voltage divider consisting of R87 and R91. The reduced voltage at the grid of the triode in side "A" drives that tube closer to cut-off and the triode in side "A" cuts off and that in side "B" fully conducts. This condition represents the second state of equilibrium.

The shorthand schematic symbol for the standard flip-flop stage is also shown on Figure 4-2. Usually the "A" side of the flip-flop is called the "O" state and the "E" side is called the "l" state. The input line on the "O" side of the flip-flop symbol indicates an input signal to set the flip-flop to "O"; the input line to the "l" side indicates a similar input to set the flip-flop to "l". When the flip-flop is in the "l" state, the "l" output shown on the "l" side of the symbol is positive, and when in the "O" state the output on the "O"

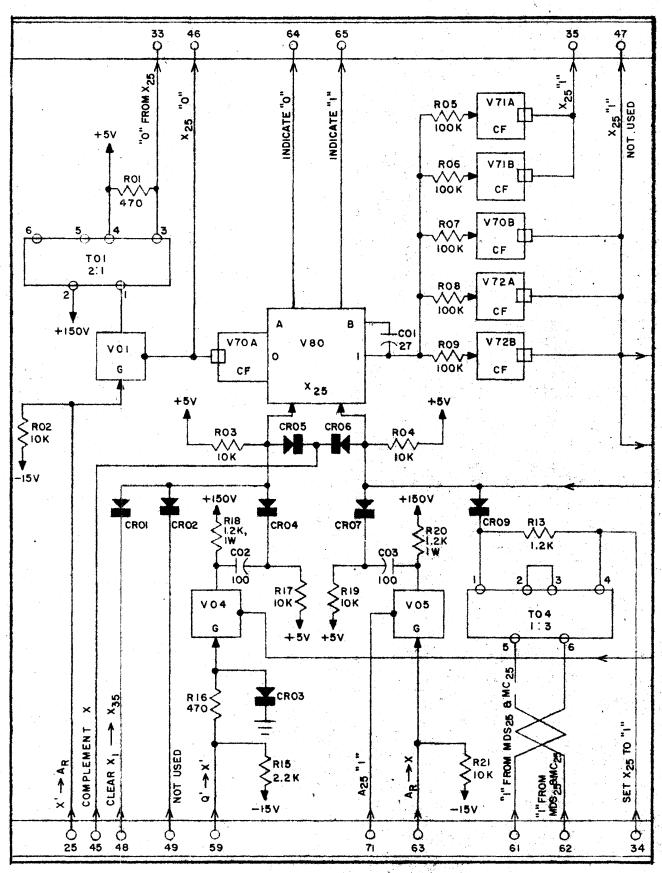

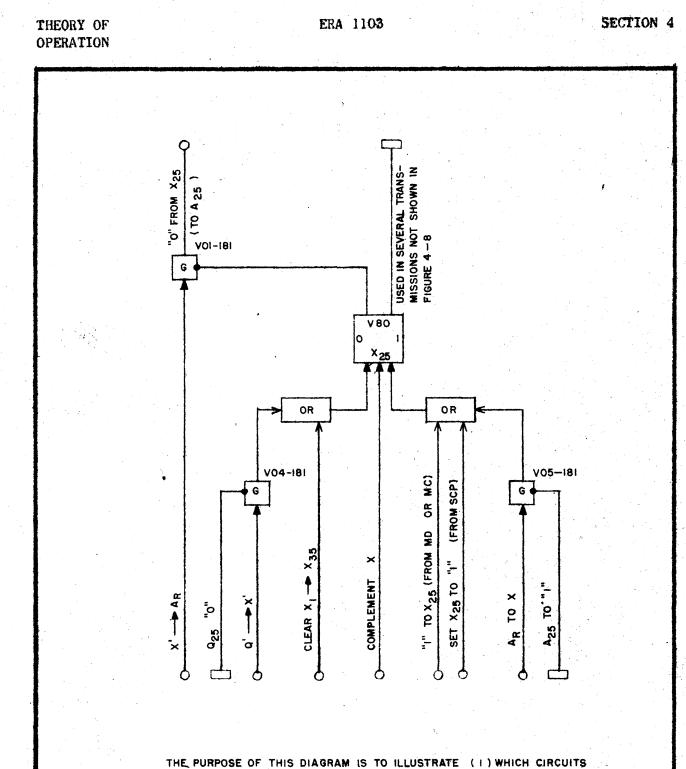

It is sometimes desirable to simply reverse the state of a flip-flop by an input signal. This is done by applying a "trigger" signal simultaneously to both input lines through isolation crystals outside the flip-flop circuit. The sample circuit shown in Figure 4-8 includes a trigger input line, connected to

Engineering Research Associates Division

CRO5 and CRO6. A negative COMPLEMENT X pulse on this line is received, through the crystals, by both sides of the flip-flop. The signal has no direct effect on the non-conducting triode, but proceeds to cut off the conducting triode. As a result, the state of the flip-flop is reversed, in the manner described above.

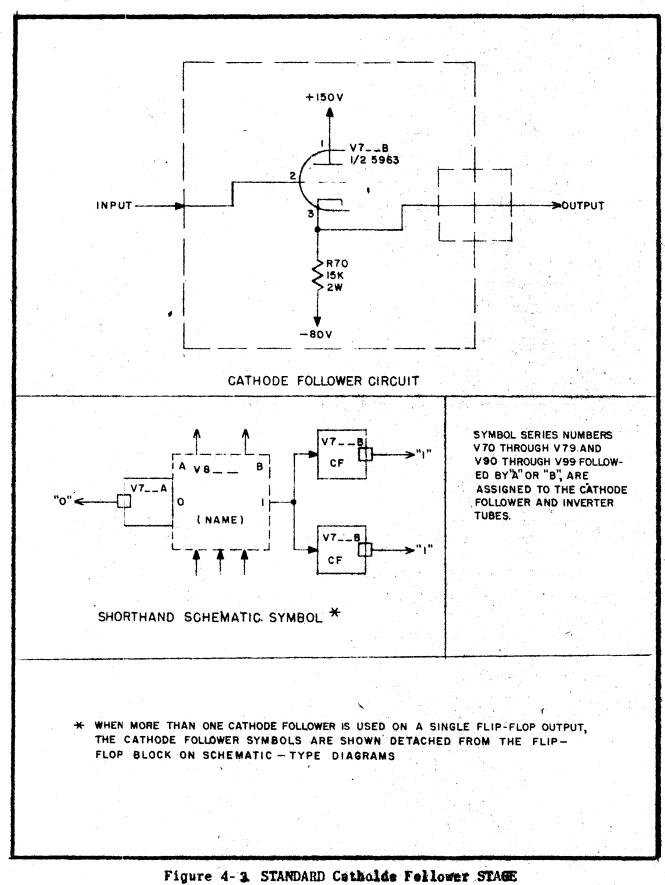

<u>2.</u> CATHODE FOLLOWER. - The standard cathode follower stage is essentially an impedance-matching or impedance-lowering device which is capable of producing power gain. A triode vacuum tube (1/25963) is employed, with the plate tied to'+150 vdc and the cathode tied through a resistance to -80 vdc. The output is taken across the cathode resistor. The circuit for this stage and its shorthand schematic symbol are given in Figure 4-3. The particular side, A or B, of the 5963 tube used is included in the tube's symbol series number.

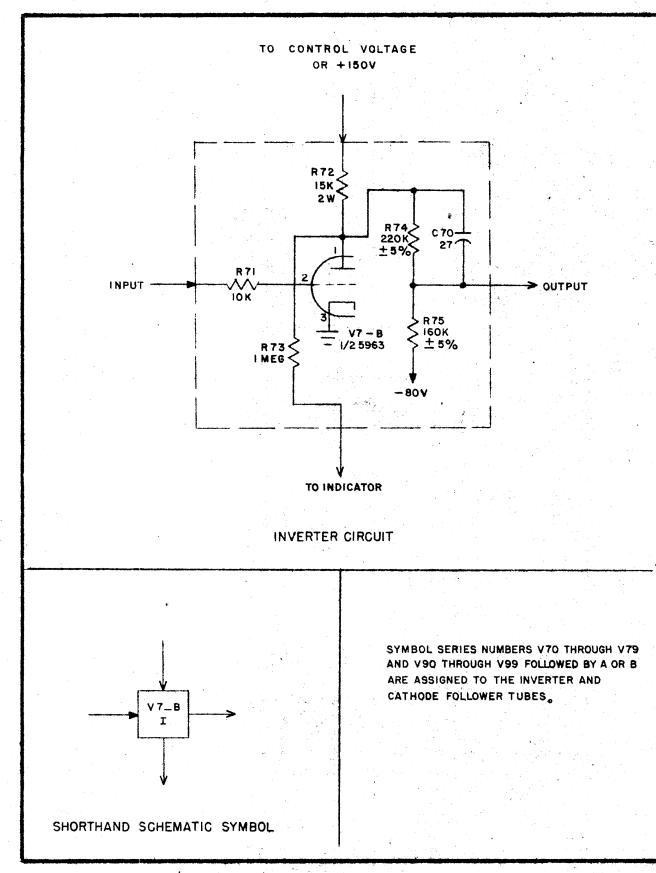

<u>3</u> INVERTER. - The standard inverter circuit stage and its shorthand schematic symbol are shown in Figure 4-4. This circuit is used to reverse the polarity of the input signal. A single triode (1/2 5963) is employed, and the particular side. A or B, of the 5963 tube is included in the inverter's symbol series number.

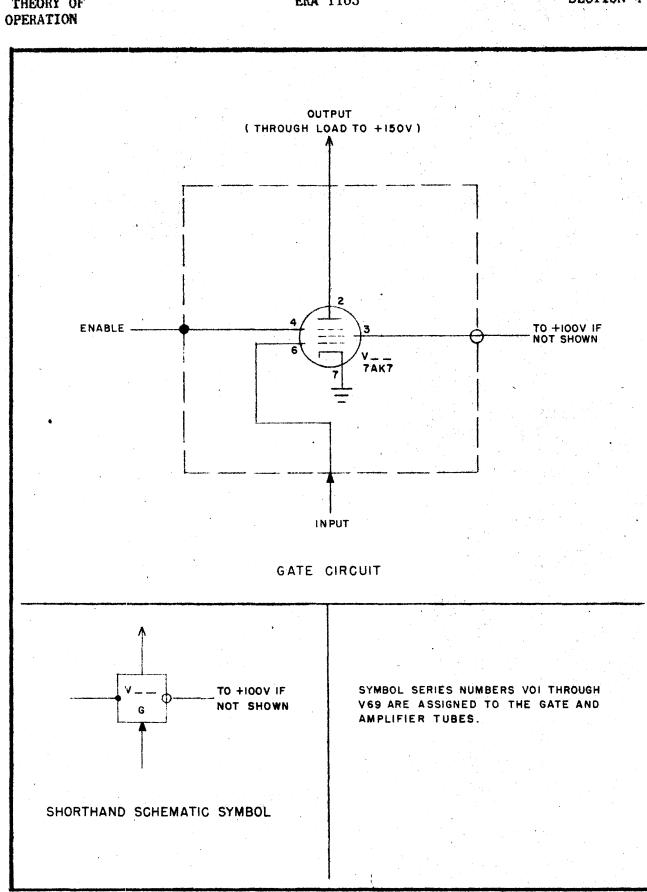

<u>4.</u> GATE. - The standard gate circuit stage shown in Figure 4-5 is a pentode (7AK7) which permits the passage of signal pulses applied to the control grid when an enabling voltage is present coincidentally on the suppressor grid. The screen grid is connected to +100 vdc if no screen grid connection is shown. The shorthand schematic symbol of this stage is also given in Figure 4-5.

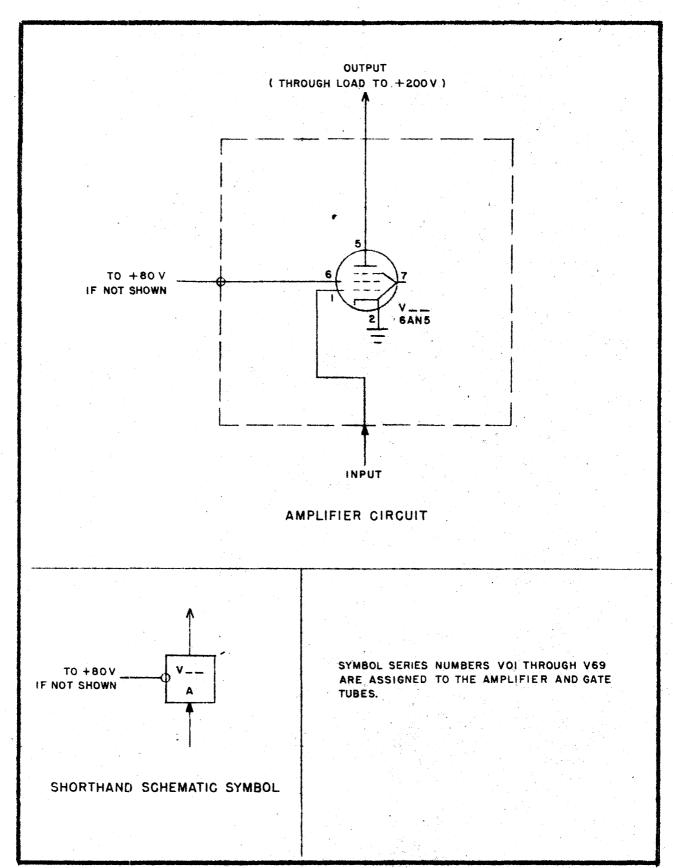

5, AMPLIFIER, - The standard amplifier stage shown in Figure 4-6 uses a 6AN5 tube. This type of amplifier is used to produce voltage gain. As shown in Figure 4-6 if the shorthand schematic symbol for this type of amplifier does not show a screen grid connection, the screen grid is connected to +80 vdc.

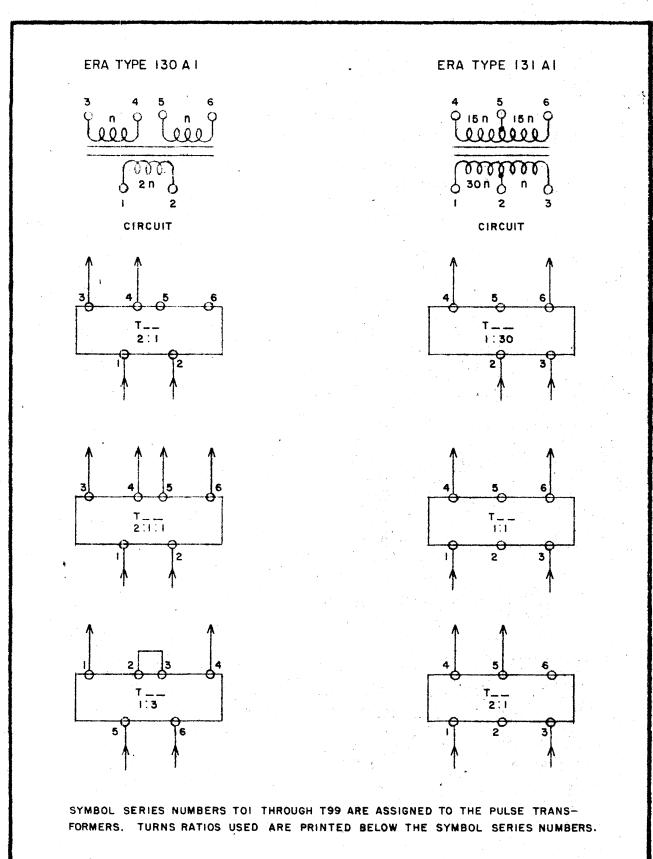

$\underline{6}_{c}$  PULSE TRANSFORMERS. - Standard pulse transformer stages are used primarily for impedance matching and phase inversion. Transformer number and winding ratios as well as the shorthand schematic symbols for each type used are shown in Figure 4-7.

$\underline{7}_{\circ}$  SUMMARY. - To illustrate how some of these shorthand schematic symbols are used, a portion of a typical schematic-type diagram is shown in Figure 4-8.

d. BLOCK SYMBOLS, - Each "block symbol" on a block diagram represents some circuit which functions as a logical element of a system, i.e., contributes in some way to "what" the system is doing. Block symbols are assigned to various circuits, therefore, on the basis of logical function. Usually different circuits performing the same functions are represented by the same block symbol. Where possible, each block symbol is identified by a tube symbol series and unit jack number so that the actual circuitry it represents can be found in the unit signal diagrams.

Figure 4-9 illustrates the block symbols used on the block diagrams of this book. Each symbol contains some type of abbreviation as G, A, FF, etc., which identifies the stage it represents. Some also contain supplemental information such as a name, which further identifies its function on the block diagram; e.g. the block symbol for Clock Pulse Distributor, Stage I flip-flop is

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

SECTION 4

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

SECTION 4

# Figure 4-4. STANDARD Inverter Stage

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

# Figure 4-5. STANDARD Gate Stege

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

PX 71671

4-14

THEORY OF

ERA 1103

SECTION 4

Figure 4-6. STANDARD Amplifier Stage

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

PX 71871

SECTION 4

Figure 4-7. STANDARD Pulse Transformer Stages

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

FX 71871

SECTION 4

Figure 4-8. Portion of a Typical Schematic-Type Diagram (with signal origins and destinations omitted.)

Remington Rand

ENGINEERING RESEARCH ASSOCIATES DIVISION

Figure 4-9. Block Symbols.

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

identified by the label "CPD-I" on the block symbol.

In the following paragraphs comments are made concerning each block symbol to acquaint the reader with its use on block diagrams.

<u>1</u>. FLIP-FLOP. - A flip-flop is a logical element which is used to store a binary "O" or "1" digit of a count or computer word, or is used in a control circuit to register control conditions. All flip-flops are assigned a specific name which suggests their function in a particular system.

<u>2</u>. GATE. - Gates are used to control the path computer signals take throughout the equipment. A gate transmits an input signal when it simultaneously receives an enable. The screen grid may be used as a second control element but if it is not used in this manner, it is connected permanently to +100 vdc.

3. AMPLIFIER, - If an amplifier does not perform a logical function, it is left off of the block diagrams, However, the screen grid of many amplifiers are connected through a "disconnect" switch to +80 vdc, so that the amplifier functions like a gate. Where this feature is used, the amplifier is shown on the block diagram.

<u>4.</u> "AND" and "OR" CIRCUITS, - An "AND" circuit is a crystal coincidence circuit; that is, an output will be produced only when signals are present on all input lines simultaneously. An "OR" circuit produces an output when a signal is received from any one or more inputs.

$\underline{5}$ . "NOT" CIRCUIT, - The "NOT" circuit produces an output signal whenever there is not a signal from the preceding stage; that is, it is an inverter which produces a positive output only when the input goes negative. Under certain conditions, if an "OR" circuit is followed by a "NOT" circuit, the two function together as an "AND" circuit.

<u>6</u>. RELAYS AND RELAY PULLERS. - Relays function in general as electromechanical switches. Relay pullers are tubes which, when conducting, energize relay coils. If a dot is present in the block symbol, the relay puller is a gas-filled tube (thyratron), and if no dot is present, it is a hard (vacuum) tube.

<u>7</u>. SHAPERS AND DELAYS. - As their names imply, these circuits are used to shape and delay pulses. Where they are included on block diagrams, the block symbol often contains additional information: e.g., for shapers, pulse width; for delays, the amount of the delay and the type of element used to effect the delay.

<u> $B_{0}$ </u> TERMINAL SYMBOLS, - The terminal symbols denote whether input and output lines are enables or pulses on block diagrams. In general, a pulse is a short-duration signal and an enable is a signal of relatively longer duration.

<u>9</u>. SUMMARY, - Figure 4-10 illustrates the block diagram representation of the circuits shown in schematic form in Figure  $4-8_{\circ}$

Stages such as inverters, cathode followers, etc., are not useful in explaining the logical function of a system and therefore are not used on block diagrams.

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

71871

Ľ

OF FIGURE 4-8 PERFORM LOGIC AND THEREFORE WOULD BE INCLUDED ON A BLOCK DIAGRAM; AND (2) HOW THESE LOGICAL CIRCUITS ARE RE-PRESENTED BY BLOCK SYMBOLS.

Figure 4-10. Block Diagram Representation of Figure 4-8.

PX 71871

## 6. STORAGE SECTION

a. GENERAL - The principle function of the Storage Section, or computer memory, is to provide the Control, Arithmetic, and Input-Output sections of the computer with the operands and instructions they require during computation. A secondary function of the computer memory is to provide temporary storage for the intermediate and final results of computations.

The Storage Section is composed of both "internal" and "external" storage. The internal storage consists of four "classes" of storage locations: magnetic drum (MD), Magnetic Core storage (MC), Q-register (Q), and Accumulator (A). Each storage position of internal storage is individually addressed. By insertion of the proper address into the Storage Address Register, any of the internal storage address locations can be made directly available for reading or writing. The external storage consists of four magnetic tape units, 0 MT, 1 MT, 2 MT, and 3 MT. Information in external storage is available only through the use of programmed computer instructions.

The principal characteristics of each of the storage systems are outlined in Table 4-1 below.

In the following subparagraphs, the Storage Address Register (SAR), the Storage Class Translator (SCT), and the Storage Class Control (SCC) circuits, which function in all references to the internal storage systems, are described first; the operation of the internal storage systems involving MD, MC, Q and A storage locations is then described; and finally the operation of the external storage system, MT, is explained.

b. STORAGE ADDRESS REGISTER - The Storage Address Register, SAR, is a 15-stage flip-flop register whose lower-order seven stages can operate as a subtractive counter. (See Block Diagram, Address Registers, Envelope \*3, Volume 7.) As a 15-stage flip-flop register SAR has two principal functions: (1) SAR is the exchange register for transmissions to and from the Program Address Counter, PAK, and for transmissions from the U-Address Counter, UAK, and the V-Address Counter, VAK; (2) SAR provides temporary storage for a 15bit storage address during internal storage references. These two functions of SAR are discussed in the following subparagraphs. The function of the seven lower-order stages of SAR as a subtractive counter, the Shift Counter (SK), are discussed in the paragraph which explains the Arithmetic Section of the computer.

(1) OPERATION AS AN EXCHANGE REGISTER. - Each of the 15 flip-flops in SAR has gate-controlled inputs to its "1" side. A set of gates in the "1" output circuits of PAK, another set of gates in the "1" output circuits of UAK, and a third set in the "1" output circuits of VAK are respectively sampled by the signals PAK-SAR, UAK-SAR, and VAK-SAR to achieve the corresponding transmissions into SAR. Generally, when transmissions from PAK, UAK, or VAK are to be carried out, the flip-flops in SAR have all been previously set to their "0" state. If SAR does not initially contain all "0"s", the transmission from PAK, UAK, or VAK will possibly set SAR to some value other than (PAK), (UAK), or (VAK). The special cases where this can occur are noted in the subparagraph which discusses SK.

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

7167]

ЪХ

• .

. Ş

# TABLE 4-1

# PRINCIPAL CHARACTERISTICS OF EACH STORAGE CLASS

| CLASS | STORAGE<br>MEDIUM                                                                                        | STORAGE CAPACITY<br>(36-bit words)                                                                                            | MAXIMUM<br>ACCESS<br>TIME                                                             | STORAGE REFERENCE<br>PROCEDURE                                                                                                                                            |

|-------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MD    | Non-Volatile:<br>Polarized areas<br>on surface of<br>continuously<br>rotating magne-<br>tizable surface. | l6,384 words<br>individually<br>addressed.                                                                                    | 34 milli-<br>seconds.                                                                 | Highest-order three bits<br>in SAR equal to 4,5,6,<br>or 7 determines drum<br>group 4,5,6 or 7. Low-<br>est order 12 bits deter-<br>mines angular position<br>on drum.    |

| MC    | Non-volatile:<br>magnetized<br>"cores" of<br>permanent magnet<br>material                                | 1024 words,<br>individually<br>addressed.                                                                                     | 8 micro-<br>seconds.                                                                  | Highest-order six bits<br>in SAR equal to 00 or<br>Ol (octal) determines<br>MC. Lowest-order 10<br>bits determines speci-<br>fic MC address.                              |

| Q     | Volatile:<br>flip-flop<br>register.                                                                      | One word.                                                                                                                     | Two<br>micro-<br>seconds.                                                             | Highest-order three<br>bits in SAR equal to 1<br>(octal) determines Q.                                                                                                    |

| A     | Volatile:<br>flip-flop<br>register.                                                                      | One word.                                                                                                                     | Six<br>micro-<br>seconds.                                                             | Highest-order three<br>bits in SAR equal to 2<br>(octal) determines A                                                                                                     |

| MT    | Non-Volatile:<br>Polarized areas<br>on surface of<br>magnetic tape.                                      | 262,144 words<br>(four tapes of<br>65,536 words<br>each). On each<br>tape, words<br>grouped in<br>blocks of 32<br>words each. | About<br>five<br>minutes;<br>transfer<br>rate of<br>about<br>222 words<br>per minute. | Words not individually<br>addressed. Words located<br>by block position.<br>Blocks accessible through<br>programmed Advance, Back,<br>Read, & Write MT instruc-<br>tions. |

Engineering Rand

In the following example it is assumed SAR is clear before transmission takes place: gates in the "1" output circuits of PAK. UAK, or VAK are sampled by the signal PAK  $\rightarrow$  SAR, UAK  $\rightarrow$  SAR, or VAK  $\rightarrow$  SAR; those gates enabled by "1" output enables from PAK, UAK, or VAK, then transmit a signal to the "1" input signal line of the corresponding stage of SAR and set the flip-flop in that stage to "1"; the effect is to change "0°s" to "1°s" in appropriate stages of SAR, so that if SAR was initially cleared to all "0°s", (SAR) becomes equal to (PAK), (UAK), or (VAK), depending on which transmission signal is received. It is important to note that in these transmissions only "1's" are transmitted.

SAR can transmit information to both X and PAK. When one set of gates in the "1" output circuits of SAR are sampled by the signal SAR $\rightarrow$ X, those gates enabled by "1" outputs from SAR transmit a pulse to the "1" input signal line of the corresponding stage in the 15 lower-order stages of X. When the other set of gates in the "1" output circuits of SAR are sampled by the signal SAR $\rightarrow$ PAK, a similar transmission to PAK occurs.

(2) OPERATION AS AN ADDRESS REGISTER. - The usual manner, in which storage addresses for internal storage references are inserted into SAR is by transmission of an address from PAK, UAK, or VAK into SAR, in the manner described in the previous subparagraph.

Another manner in which addresses are inserted into SAR is by special Command Timing Circuit (CTC) signals which set or clear SAR flip-flops, During one Command Timing Sequence, signals are initiated to change (SAR) to register either the first MC address, 00000, or the second MD address, 40001. If the  $F_1$  switch on the Supervisory Control Panel (See Block Diagram, CTC, Envelope #4, Volume 7) is set to MC, a CLEAR SAR signal from CTC clears all SAR flip-flops to "O". However, if this switch is set to the MD position, SAR14 and SAR0 are set to "1" and SAR1 through SAR13 are cleared to "O" so that the address 40001 is in SAR.

The signal CLEAR SAR is also produced, either by an INTERNAL STORAGE RE-SUME signal received from the Pulse Distributor Control after each MD, MC, Q, and most A references, or by a CLEAR SAR signal issued directly by the Arithmetic Register Access Control. This is done to prepare SAR for receipt of the next address.

The possible addresses that can be formed by a 15-bit number and hence can be inserted into SAR are shown in octal notation in Table 4-2 below. Note that some possible addresses are not assigned to any of the four storage classes. These unassigned addresses, if inserted into SAR, will produce an SCC Fault and stop computer operation.

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

ADDRESSES

ERA 1103

## TABLE 4 – 2 ASSIGNMENT OF ADDRESSES

ASSIGNED TO

00000-01777 MC Storage Addresses Unassigned 02000-07777 Q-Register Address (first digit only is significant; the 1 - - - other digits may be assigned any value.) Accumulator Address (first digit only is significant; the 2---other digits may be assigned any value.) Unassigned 30000-37777 MD, Group 4 Addresses 40000-47777 MD, Group 5 Addresses 50000-57777 60000-67777 MD, Group 6 Addresses MD, Group 7 Addresses 70000-77777

The storage addresses assigned to each storage class form a closed consecutive set; i.e., each address of each class may be used to generate the next address of the set; the last address of each set can be used to generate the first address of the set.

This "closed loop" operation is explained in the text for UAK, VAK, and PAK.

When an internal storage reference operation is initiated, the "O" and "1" outputs of SAR are employed to determine not only which storage class (MD, MC, Q, or A) is involved, but, in the case of MD and MC, which <u>specific</u> storage location in the selected class is desired. The "O" and "1" outputs of the five higher-order stages of SAR are used to initiate a reading or writing operation in the proper storage system. If the referenced address belongs to the MD storage class, SAR stages SAR<sub>0</sub> through SAR<sub>14</sub> are used in the MD system to locate the specific MD address desired. If the referenced address belongs to the MC storage class, SAR stages SAR<sub>0</sub> through SAR<sub>9</sub> are used in the MC system to locate the specific MC address desired. If the referenced address belongs to the Q or A class, the lower-order bits are ignored because Q and A both store only one word.

After an internal storage reference has been completed, the CLEAR SAR signal prepares SAR for the receipt of new data, as described previously in this sub-paragraph.

c. STORAGE CLASS TRANSLATOR. - The Storage Class Translator (SCT), shown on the Block Diagram, Storage Class Control, Envelope #2, Volume 7, is a group of "AND" circuits which interpret the contents of the five highest-order bits of the address held in SAR and produce storage class enables for the Storage Class Control (SCC), the Arithmetic Register Access Control (ARAC), and the Fault Detector.

The storage class enables produced by SCT for the various possible combinations of bits in the higher-order stages of SAR are listed in Table 4-3 below. The Storage Class Translator does not receive outputs from the 10 lower-order stages of SAR.

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

### $\cdot$ TABLE 4-3

# STORAGE CLASS TRANSLATION

| SAR STAGE |    |     | ADDRESS      | RESULTING STORAGE |          |                       |              |

|-----------|----|-----|--------------|-------------------|----------|-----------------------|--------------|

| 14        | 13 | 12  | 11           | 10                | RAM      | NGE SPECIFIED (Octal) | CLASS ENABLE |

| 0         | 0  | 0   | 0            | 0                 |          | 00000 - 01777         | MC           |

| 0         | 0  | 1   |              | -                 |          | 10000 - 17777         | Q            |

| 0         | 1  | 0   | . <b>a</b> t | -                 |          | 20000 - 27777         | А            |

| 1         |    | -   | ***          | -                 |          | 40000 - 77777         | MD           |

| "1"       | in | any | stag         | e , SAI           | 10-SAR14 | 02000 - 77777         | NOT MC       |

The SCT enables MC, Q, A, and MD are used in SCC during SCC sequences to direct INITIATE READ and INITIATE WRITE commands from the Command Timing Circuits (CTC) to the proper internal storage system, and are used in the Arithmetic Register Access Control to control the clearing of A during certain instructions.

All five SCT enables (MC, Q, A, MD, and NOT MC) are sent to the Fault Detector where they are used to detect erroneous storage class references.

d. STORAGE CLASS CONTROL - The Storage Class Control (SCC), shown on the Block Diagram of the Storage Class Control, Envelope #2, Volume 7, consists basically of the following four flip-flops: Initiate Read, Initiate Write 0-35, Initiate Write 0-14, and Initiate Write 15-29. Each of these has a series of gates associated with its "1" output circuit. The basic purpose of SCC is to carry out short sequences which initiate reading or writing operations in the storage class referenced by SAR.

SCC performs an SCC Initiate Read Sequence for MC, Q, A, or MD after its Initiate Read flip-flop is set to "1" by an INITIATE READ signal from CTC. The sequence initiates a reading operation in a particular storage system, depending on the type of SCT enables (MC, MD, Q, or A) present on the gates associated with the "1" output circuit of the Initiate Read flip-flop. Similarly, SCC performs one of the three writing operations after an INITIATE WRITE O-35, INITIATE WRITE O-14, or INITIATE WRITE 15-29 signal from CTC sets the Initiate Write O-35, Initiate Write O-14, or Initiate Write 15-29 flip-flop in SCC to "1". An Initiate Write Sequence initiates a writing operation in one storage system, depending on the SCT enables which are present on the gates associated with the "1" output circuit of these flip-flops.

(1) SCC INITIATE READ SEQUENCES. - SCC executes the following four SCC Initiate Read sequences: SCC Initiate Read MD, SCC Initiate Read MC, SCC Initiate Read A, and SCC Initiate Read Q. These sequences are listed in tabular form in Appendix B, Page B-58, Volume 2. Each sequence is begun by the INITIATE READ signal from CTC. The particular sequence executed for any given

Encineering Research Associates oursion

.

internal storage reference depends on which of the gates associated with the "1" output of the Initiate Read flip-flop are enabled by SCT.

As an example of how all SCC Initiate Read sequences are executed, the sequence is described below for the case where an MD address is held in SAR. (See Block Diagram, SCC, Envelope #2, Volume 7.) An MD address held in SAR causes SCT to enable the following gates in SCC: V07-30153, V02-30153, V06-30123, V06-30143, and V05-30153. When an INITIATE READ signal is produced by CTC, the SCC Initiate Read flip-flop V80-30143 is set to "1", and gate V08-30143 is thus enabled. The next CONTROLLED CLOCK PULSE that is produced passes through gate V08-30143, clears the Initiate Read flip-flop, samples gates V04-30143, V09-30143, V05-30143, V06-30143, and V05-30153, and is sent to the Fault Detector. Gates V06-30143 and V05-30153, enabled by the MD enable, issue INITIATE READ MD and INITIATE MD REFERENCE signals to initiate a reading operation in the MD system.

In a manner similar to that described above, INITIATE READ MC, INITIATE READ A, and INITIATE READ Q signals are produced for MC and ARAC when MC, A, or Q addresses, respectively, are in SAR.

(2) SCC INITIATE WRITE SEQUENCES. - There are six possible SCC Initiate Write sequences for MD and MC, as follows: SCC Initiate Write MD (0-35), SCC Initiate Write MD (0-14), SCC Initiate Write MD(15-29),SCC Initiate Write MC (0-35), SCC Initiate Write MC (0-14), and SCC Initiate Write MC (15-29). The 0-35 sequences initiate the writing of 36-bit words in MC and MD locations, and the 0-14 and 15-29 sequences initiate writing operations in only the v-address and u-address portions of storage locations, respectively. For example, these "partial writes" are used, in execution of the Insert u Address (15uv) and Insert v Address (16uv) instructions, to alter execution addresses in a programmed routine.

No partial writing operations can be used in Q and A. For this reason, only two SCC Initiate Write sequences are possible for Q and A, as follows: SCC Initiate Write Q and SCC Initiate Write A.

Each SCC Initiate Write sequence is executed in a manner similar to the SCC Initiate Read MD sequence described in the previous subparagraph. The specific steps are described in detail in Appendix B, Pages B-59 through B-61 in this volume.

It should be particularly noted that SCC does not initiate any partial read operations in any of the internal storage systems, and that the SCC initiates partial writing operations only in MD and MC.

The following outline of events summarizes the basic functions of SAR, SCT, and SCC during internal storage references:

- (1) A 15-bit storage address is held in SAR during every internal storage reference.

- (2) Outputs from the five higher-order stages of SAR are translated by SCT to select MD, MC, or Register Storage as the memory system which is to function.

# Brancestory tom. WRennel. Engineering Research Associates division

- (3) One of the SCC Initiate Read or SCC Initiate Write sequences is performed which initiates the desired operation in the storage system of the selected storage class.

- (4) If MD or MC is involved, the output of lower-order stages of SAR are also used to determine the particular MD or MC location referenced.

- (5) When the desired operation has been carried out in the exact memory location specified, SAR is cleared and thus prepared for use in another storage reference.

e. MAGNETIC DRUM STORAGE SYSTEM. - The Magnetic Drum Storage System (MD) provides the 1103 Computer System with a non-volatile, medium-access storage memory. Each of the 16,384 36-bit storage locations in MD is individually addressed and is available for reading or writing once each drum revolution. Storage addresses 40000 through 77777 (octal) are assigned to MD.

The MD Storage System (See Block Diagram, Magnetic Drum Storage System, Envelope #2, Volume 7) is composed of four principal parts, as follows: (1) the Magnetic Drum Assembly which includes the storage medium, a coated surface on a continuously rotating aluminum cylinder (known as the magnetic drum) which receives computer words during writing and makes them available for reading once during each revolution of the drum, and the transducing elements, dualpurpose magnetic reading-and-writing heads which transfer data to and from the storage positions with which they are associated; (2) the Clock Pulse Distributor (CPD) which receives 500 kc signals from the Timing Pulse Multiplier circuit when the drum is used as the basic clock source, and issues timing signals CP-0, CP-1, and CP-3 to the MD system; (3) the Magnetic Drum Locating Circuits which function primarily to notify the MD Access Control when a referenced storage location has been located and positioned for reading or writing; and (4) the Magnetic Drum Access Control which directs the transfer of words into or out of the drum when the referenced storage location is properly positioned.

(1) MAGNETIC DRUM ASSEMBLY. - The Magnetic Drum Assembly consists of two principal elements: the rotating cylinder (or drum), and the magnetic reading and writing heads.

The cast-aluminum drum (see Plate 5-17, Volume 6) is 17 inches in diameter and 11.875" long. It is taper-fitted and locked to a steel shaft which in turn is mounted on a cast-aluminum base and driven at 1725 rpm by a 220 vac. 3 phase, 3/4 hp motor. The machined drum surface is coated with magnetic iron oxide, except at one end where it is emcircled by a narrow soft steel band. A cast aluminum head-mounting bracket fits over the top of the drum and fastens to the supporting base.

The head-mounting bracket contains inserts which receive the magnetic heads. Details of the magnetic head assembly are shown in Plate 5-20, Volume 6. These inserts are arranged for space considerations so that the heads are mounted in the bracket in a spiral fashion. A lateral spacing of  $1/16^{\circ}$  between adjacent heads is maintained by means of the spiral arrangement.

ERGMANNESTRATION. REARCH ASSOCIATES UNITED

The mechanical "setting" of each head is accomplished by a differential thread principle. When a head is properly set, its core-gap is approximately 0,002 inch from the drum surface.

Once the head has been set, the head cable is connected by fitting the fiveconductor plug of the head cable into the head barrel and tightening the coupling flange firmly. The entire MD Assembly is shown installed in Plate 5-19, Volume 6.

(2) PRINCIPLES OF MAGNETIC DRUM STORAGE.-- Each magnetic head contains a single winding on a ferrite core. In writing, a current pulse of a given polarity is sent through the winding, setting up a magnetic field. The pulse polarity governs whether a "O" or a "l" is to be written. The flux of the magmetic field fringing around the gap of the core magnetizes to saturation that portion of the drum surface under the gap at that instant. The polarity of the magnetized area agrees with the pulse polarity applied to the head winding, and thereby can be later distinguished as a "O" or a "l" during reading operations. Amplifiers in the reading circuits receive signals from areas storing "O's" as well as from those storing "l's", but produce outputs only when "l's" are read.

The narrow band on the coated storage surface of the drum which passes beneath one head as the drum revolves is called a "track". Tracks on this surface exist only in concept, i.e., the coated surface is not physically divided, but can be thought of as discreet narrow bands, one for each head. However, the two tracks on the soft steel band on the end of the drum exist physically. The outer track, or "timing track", is uniformly knurled with V-shaped notches which are spaced 80 per circular inch. The inner track is called the "mark track" and it contains a single "zero index" notch. These two permanent tracks are used for control purposes. Unlike the other heads, the heads associated with the two permanent tracks perform only reading operations.

Provision is made for three read heads (one for the timing track, one for the mark track, and one spare), and 175 read-write heads (including 31 spares) for the tracks on the coated surface; 144 of the read write heads and their associated tracks are divided into 4 groups of 36, called Group 4, Group 5, Group 6, and Group 7.

Each group of read-write heads has 36 sets of reading and writing circuits, each of which is associated with one of the 36 heads of the group. In every reading or writing operation sequence, one part of the operation selects which group of heads is to read or write; another part selects the angular position of the drum at which these heads are to function.

The timing track and mark track are used in connection with the angular position selection. The timing track notches, spaced 80 per circular inch, are used to identify discreet angular positions of the drum; i.e. when the timing track head senses a notch, it produces a TIMING PULSE signal. The TIMING PULSES are produced at a rate of 125 kc. Each TIMING PULSE results in a signal which notifies MD Location Control that an angular position will presently be correctly positioned for reading or writing. The single notch on the mark track is called a zero index notch because it marks the effective beginning of the timing track. It establishes a reference point during each drum revolution from which angular positions are counted. The first 4096 notches read from the timing track after the zero index notch on the mark track is read define the

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

4096 usable angular positions of the drum. All other positions, i.e., those between angular position 4095 and angular position 0, are called the "dead space" on the drum.

Since there are 4096 angular positions of the drum at which each of the four groups can read or write, there are a total of 16,384 locations, or storage addresses, available. Each MD storage address is uniquely defined by specifying what group of heads writes into it or reads from it, and at which angular position of the drum it is located.

The portion of each track that is positioned beneath one magnetic head during one angular position of the drum is called a "cell". It is convenient to think of each of the 36 heads of a group as writing into or reading from one cell beneath it at discreet angular positions of the drum.

The return-to-neutral method of recording is employed; i.e., all the cells of the drum are initially unmagnetized. During writing operations both the "O's" and "l's" of the word to be stored are written; during reading only the "l's" are read to  $X_{\circ}$

(3) CLOCK PULSE DISTRIBUTOR, - The Clock Pulse Distributor (CPD) uses 500 kc CLOCK PULSES to produce CP-0, CP-1, and CP-3 pulses for controlling the MD operations,

The 500 kc CLOCK PULSES are developed by the Timing Pulse Multiplier circuit, shown in the lower right corner of the Block Diagram, MD Storage System. When manual selections are made so that the drum is used as the basic source of CLOCK PULSES, the 125 kc TIMING PULSES from the drum timing track are recirculated through this circuit. Each TIMING PULSE entering the circuit is delayed by two microseconds, then fed back into the circuit. As a result, the output of this circuit is a sequence of 500 kc MD CLOCK PULSES. These pulses are used not only in the MD Storage System, but also in the Clock Pulse Distributor as a basic source of computer clock pulses.

For convenience the operation of the Timing Pulse Multiplier and the Clock Pulse Distributor are best described together. The Timing Pulse Multiplier and the Clock Pulse Distributor consist of two flip-flops (CPD I and CPD II), a two microsecond delay circuit WO1-60054, six gates, and several coincidence circuits. Initially, CPD I and CPD II are set to "O", and the recirculation gate V02-60054 is enabled. When the drum is selected as the clock source, a MULTI-PLIER ENABLE is supplied to gate V03-60054, from the normally-closed contacts of the Select Osc relay, K30018. The first TIMING PULSE to enter the Multiplier through gate VO3-60064 will emerge after a two microsecond delay as an MD CLOCK PULSE. This MD CLOCK PULSE is then sent externally to the Clock Rate Control (CRC), a part of the Master Clock System, Within the Multiplier and Distributor each MD CLOCK PULSE is used to probe Distributor gates V04-60073, V06-60073, and V07-60073, to advance the Distributor flip-flops, and to probe the recirculation gate V02-60054. The first MD CLOCK PULSE, issued two microseconds after a TIMING PULSE, finds Distributor gate V04-60073 enabled and produces CP-0. It also triggers CPD II to "1", and passes through the recirculation gate VO2-60054. (It does not change CPD I since gate VO1-60034 is not yet enabled,) After a two microsecond delay, this first MD CLOCK PULSE is issued again to CRC by the delay circuit as another MD CLOCK PULSE. This second MD CLOCK PULSE finds Distributor

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

gate V06-60073 enabled and produces CP-1. It passes through gate V01-60054 (enabled since CPD II is a "1"), triggers CPD II back to "O", and triggers CPD I to a "1". It recirculates, and two microseconds later it emerges as the third MD CLOCK PULSE. This third MD CLOCK PULSE is sent externally to CRC as were the other two, but internally it finds all three Distributor gates and gate VOI-60054 disabled, so it merely triggers CPD II to a "1" and is recirculated. After a two microsecond delay it emerges as the fourth MD CLOCK PULSE. Like the others, this fourth MD CLOCK PULSE is sent externally to CRC. Internally it finds Distributor gate V07-60073 enabled and passes through as CP-3. Since CPD II and CPD I were both set to "1" by the previous MD CLOCK PULSE, gate V02-60054 is disabled during CP-3, so that the fourth MD CLOCK PULSE is not recirculated. Its only function in the Distributor is to trigger both CPD II and CPD I to "O". At the same time that CP-3 is produced, another TIMING PULSE arrives from the drum and the above sequence is repeated. As a result of the above operations. the Master Clock System receives 500 kc MD CLOCK PULSES and the MD Access Control receives CP-0, CP-1, and CP-3 signals. The numerals 0, 1, and 3 after the letters "CP" signify the relative time of occurrence of these pulses in 500 kc CLOCK PULSE periods: i.e., CP-0 and CP-1 are separated by two microseconds, and CP-1 and CP-3 are separated by four microseconds.

(4) MAGNETIC DRUM LOCATING CIRCUITS. - These circuits are used in each MD reference to find the MD storage location specified by (SAR), and to generate the proper signals for reading or writing when the drum is positioned in that location. These circuits are shown in the lower left quarter of the Block Diagram of the MD Storage System.

The complete storage address of a particular location in MD is specified by a 15-bit number. The three higher-order bits specify the group number, which may be 4, 5, 6, or 7. The 12 lower-order bits specify one of the 4096 angular positions of the drum. At the time a storage reference is made, a 15bit storage address is held in the Storage Address Register, SAR. One part of the MD Locating Circuit is a Group Selection Circuit which performs the group selection specified by the group bits of the storage address. The other part of the MD Locating Circuit searches for the angular position specified by the storage address, and generates a COINCIDENCE PULSE when the correct angular location is properly positioned for reading or writing.

The Group Selection circuit is composed of a group detector, a group selector, and a group translator. The group detector is composed of four gates and several coincidence circuits. Gates V05-30203 and V06-30203 receive an INITIATE MD REFERENCE signal from SCC during every MD reference. If the group which is to function in the current MD reference is the same group that functioned during the last MD reference (i.e., if SAR<sub>12</sub> and SAR<sub>13</sub> = GS<sub>1</sub> and GS<sub>2</sub>), these gates are disabled and the group detector does not initiate any change in group selection. But if the current address in SAR specifies a group different from the group which last functioned in an MD reference, either gate V05-30203, or gate V06-30203, or both will be enabled and their outputs will trigger group selector flipflops GS<sub>1</sub> and GS<sub>2</sub> to register the correct group selection. The outputs of the GS<sub>1</sub> and GS<sub>2</sub> flip-flops are combined in coincidence circuits in the group translator. Depending on which group is selected, a GROUP 4, GROUP 5, GROUP 6, or GROUP 7 enable is produced. Each of these enables is sent to gates in the reading and writing circuits of the group of heads to which it corresponds. For example, if a GROUP 4 enable is produced, it enables gates in the reading

Exercise Record Record Exercise Constants Constants

1

and writing circuits of each head in Group 4. Once selected, a particular GROUP enable is present until a new group selection is made.

If a change in the group selection is required for a reading operation, it is necessary to delay reading by about 32 microseconds to allow the circuitry to recover from transients introduced by the group switching operation. No corresponding problem exists for the writing operation. When a read reference is made to MD, gates VO1-30203 and VO4-30203 in the Group Detector are pulsed by the INITIATE READ MD signal from SCC. If the currently referenced group of heads is the same as the last group which functioned, gate VOI-30203 will be enabled and the SCC signal will produce an INITIATE READ signal for MDAC. If a switching of groups is required in the current MD reference, gate V04-30203 will be enabled and the SCC signal will produce an INITIATE DELAYED READ signal for MDAC. This latter signal sets the Initiate Delayed Read flip-flop in MDAC to "1". The "1" output of this flip-flop initiates a delay of approximately 32 microseconds, and thereby prevents any attempt to probe for coincidence (and hence read) until the reading amplifiers have had a chance to recover from the transients generated by switching heads. If an INITIATE READ signal is produced, the above delay is not initiated.

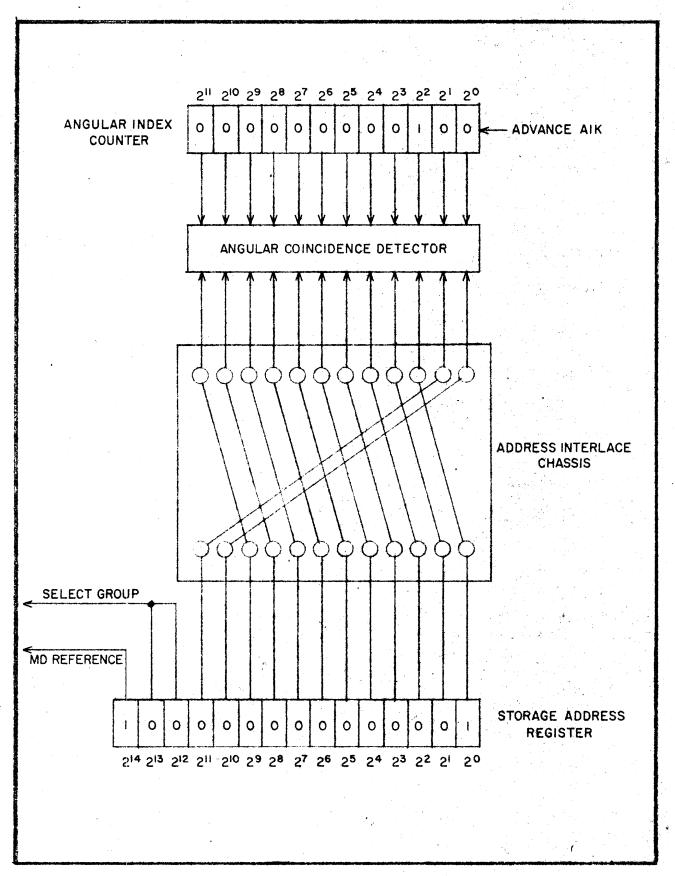

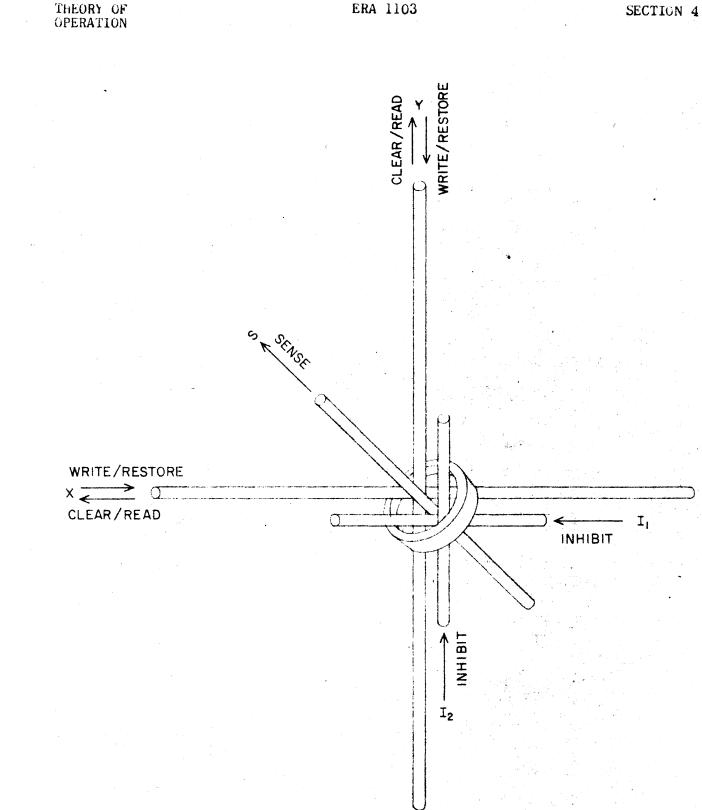

The remainder of the MD locating circuits are the Address Interlace Chassis, an Angular Coincidence Detector, an Angular Index Counter (AIK), and a Location Control circuit, (See Block Diagram and Figure 4-11.) These function to select the angular position on the drum which is referenced by lower-order 12-bits of the storage address held in SAR. The Address Interlace Chassis, depending on its wiring arrangement, translates the 12 angular position bits of address in SAR in such a manner that if addresses with consecutive angular positions are inserted into SAR, they become coincident with every fourth, eighth, sixteenth, thirty-second, or sixty-fourth angular position on the drum, rather than with physically adjacent angular positions. The Angular Coincidence Detector compares the count in AIK (a 12-stage binary counter) with the interlaced count from SAR. Location Control consists of three flip-flops (Preset, Advance AIK, and Coincidence Lockout) and their associated gates. Location Control regulates the advance of AIK and the probing of the Angular Coincidence Detector.

In every MD reference, the 12 lower-order bits in SAR are connected through the Address Interlace Chassis to the Angular Coincidence Detector. As the drum rotates, TIMING PULSES from the timing track head are produced which identify or define each successive angular position of the drum. Each of these TIMING PULSES results in a signal which causes the Angular Index Counter (AIK) to advance by one, so that AIK maintains a count which indicates the angular position of the drum to be properly positioned next for reading or writing. When, during reading or writing operations, the angular position of the drum indicated by (AIK) matches the referenced angular position from the Address Interlace chassis a COINCIDENCE PROBE signal detects this condition and the Coincidence Detector generates a COINCIDENCE PULSE for MDAC. The COINCIDENCE PULSE results in the referenced reading or writing operation being performed in exactly the referenced angular location.

Five types of Address Interlace Chassis are provided with the 1103 system: one chassis each for 4, 8, 16, 32, and 64-interlaces. However, only one of these is inserted into the equipment at any one time. Each, in effect, alters the angular position of consecutive storage addresses from Computer Control in

Remington Rand ENGINEERING RESEARCH ASSOCIATES DIVISION

ERA 1103

THEORY OF OPERATION

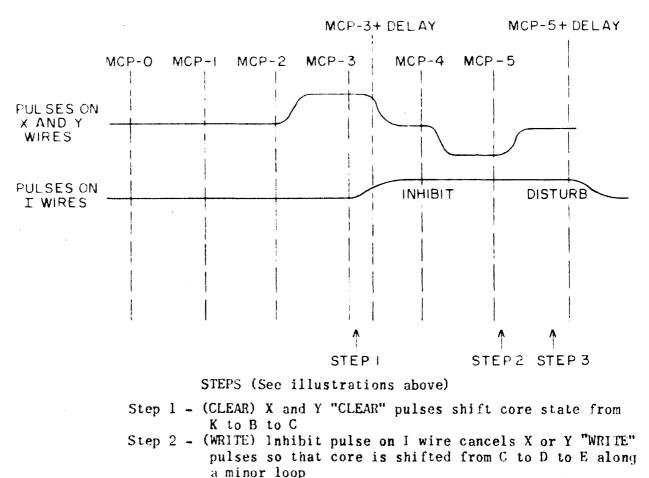

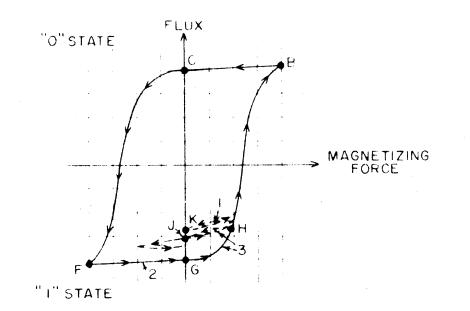

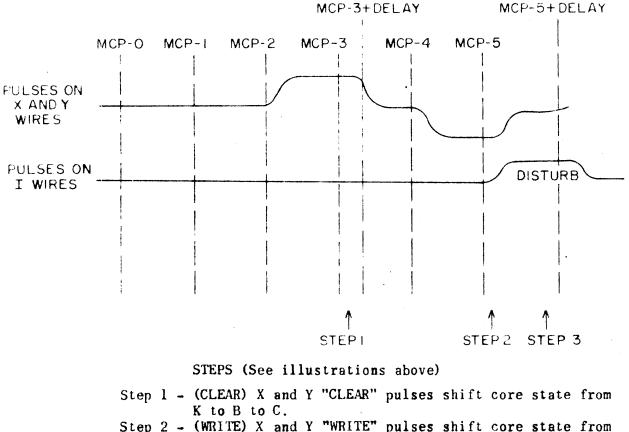

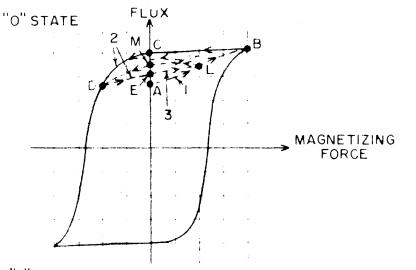

such a manner that they will be coincident with different sequences of angular positions on the drum. For example, the 4-interlace Address Interlace Chassis will translate the angular positions specified in consecutive storage addresses received from SAR so that they are coincident with every fourth angular position on the drum, rather than with the physically consecutive angular positions. If the 8-interlace Address Interlace Chassis is used, then coincidence is obtained from every eighth angular position on the drum and so on. A spare Address Interlace chassis is also provided which can be wired to make angular positions of consecutive addresses in Computer Control coincident with the consecutive, or physically adjacent, angular positions on the drum. In summary, Address Interlace Chassis function to assign an order or sequence to the angular positions on the drum which are to be coincident with consecutively numbered angular positions from Computer Control.